各种高速AD采集卡大体硬件功能相同时,使用不同的FPGA时,如V5和V6系列,单就高速AD采集卡的逻辑和性能来说,带来一些差异。通过简单对比北京坤驰科技有限公司的使用了交织采样技术的高性能同系列高速AD采集卡,就会很清晰的得出相关差异分析结果。

1,例如其ADQ系列高速AD采集卡的板上FPGA分为V5和V6两个系列,在触发功能上大部分原理是相同的,但FPGA不同的物理结构也导致了一些差异,那么差异在哪呢?

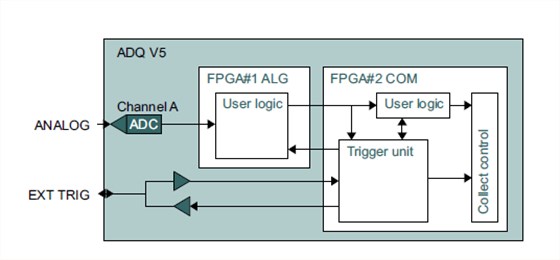

首先,V5有两个FPGA模块,触发模块在FPGA #2上, 实现触发输出及其他与数据采集触发相关的功能,例如在波形平均功能使用时,也需要FPGA #2上的触发模块将产生的触发信息传到FPGA#1,2块FPGA的物理结构给触发带来了传输、处理上的相对限制。还有,V5上触发输入和输出共用相同的物理连接器。

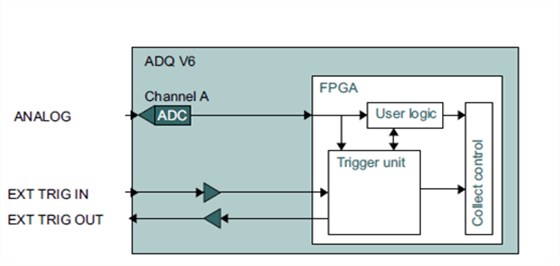

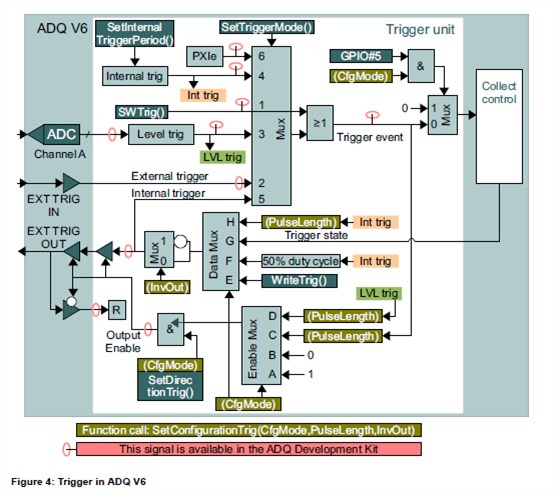

对比之下,V6,只有一块更为强大的FPGA,各功能模块之间的通信比V5更为直接高效,触发输入和触发输出使用不同的连接器,大大增加了灵活性。

两者触发逻辑对比如下两图:

A,V5系列

B,V6系列

2,触发模式:

触发器可以选择两种主要的触发模式:

1,触发的数据流模式(triggered streaming)-适合大化的利用数据传输到主机的速度

2,多段记录模式(multi record mode)-适合大量数据的实时采集

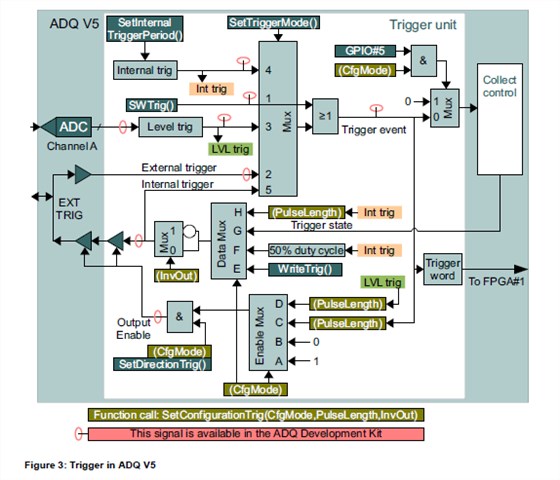

3,触发框图

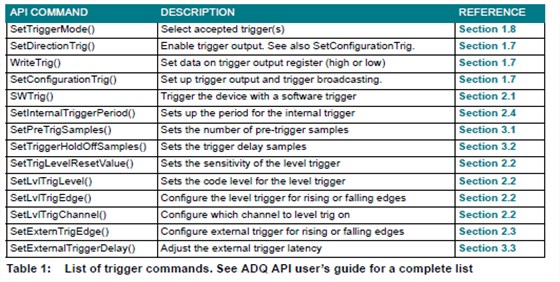

4,触发相关的API指令

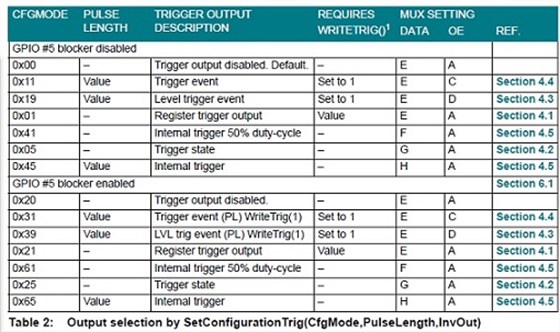

5,触发输出设置参考表格:

Table 2列出了触发的相关设置,CfgMode参数控制了触发输出设置和GPIO#5的输入触发模块功能的设置。PulseLength参数为脉冲长度设置。

Figure 4中的InvOut是反向触发输出参数。

使用SetConfigurationTrig()时,不需使用SetDirectionTrig()指令;WriteTrig()为寄存器触发设置硬件寄存器的位数。

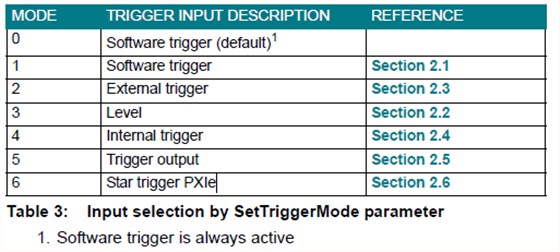

触发输入控制参考表格

6,采集控制设置

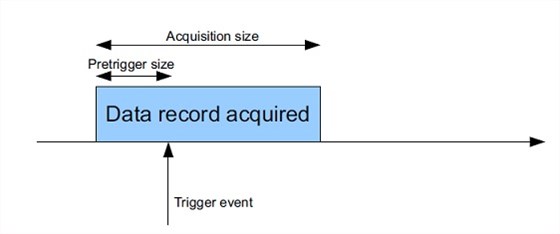

6.1 Pre-trigger

注,数据流模式(streaming mode)下,预触发的长度是有限的,对比之下,多段记录模式下(multi-record)高可达234个采样点。

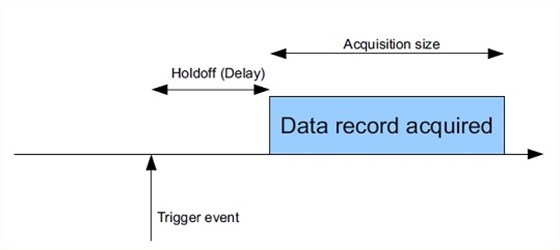

6.2 Hold-off (Delay)

延迟长度高可达234个采样点(取决于板卡模式)

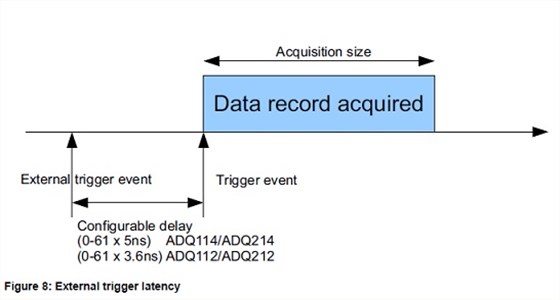

6.3 可调节外部触发延迟(ADQ V5)

当数据从ADC经由电路传到用户逻辑模块进行处理时,延迟长度可能因电路原因发生变化。为了补偿这个变化,外部触发器可相对延时基线延时一定的采样点数。如下图,这种效果与触发hold-off模式较为相似。是hold-off模式与用户逻辑之间中间处理操作。

电话咨询

电话咨询 产品中心

产品中心 在线留言

在线留言 关于坤驰

关于坤驰