数字IO卡是采集数字IO信号的仪器,其功能类似于逻辑分析仪。北京坤驰科技公司的M2i.7011数字IO卡有16、32与64bit版本可选,且在16bit与32bit版本中高采样率可达125MS/s。板卡具备高2GB板载内存,在FIFO下,板卡持续流模式传输速度可达160MS/s,可满足大部分使用需求。

在本次应用实验中经过对过程中问题的分析、解决,实现了对蓝牙信号的采集。

1environment setup

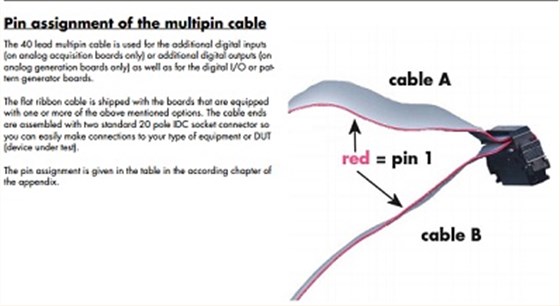

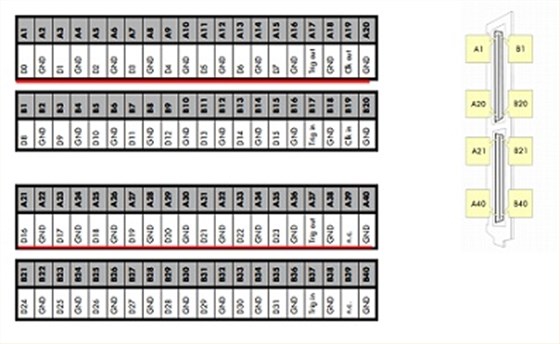

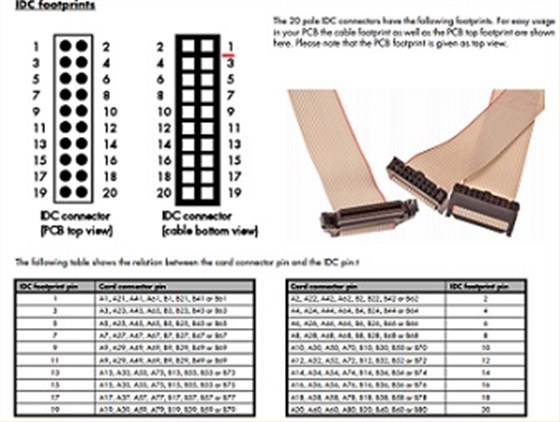

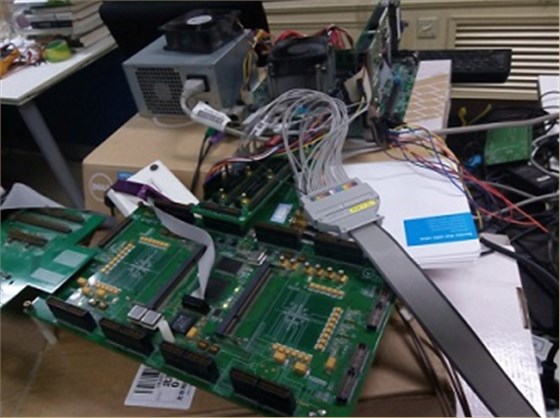

我们可以根据m2i.7011的datasheet中的管脚定义,可以清晰的找到数字IO信号、时钟CLK信号、数字地信号GND等。

基于m2i.7011是大32bit的IO可以使用,用户需要20bit的数字IQ信号,其中包括I路信号10bit,Q路信号10bit,还有1路clk输入信号,外加GND数字地信号。

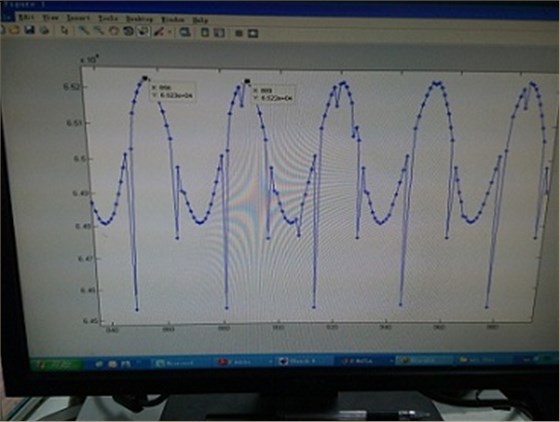

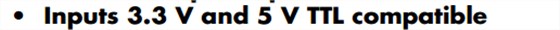

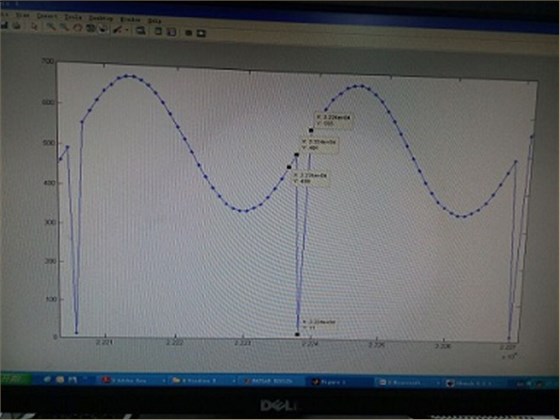

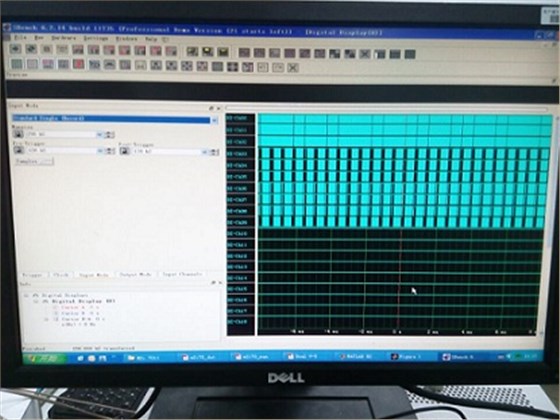

下图是ADC采集的信号,用xilinx的chipscope软件抓的ADC芯片量化出来的数据,可以看到采集的波形很平滑。

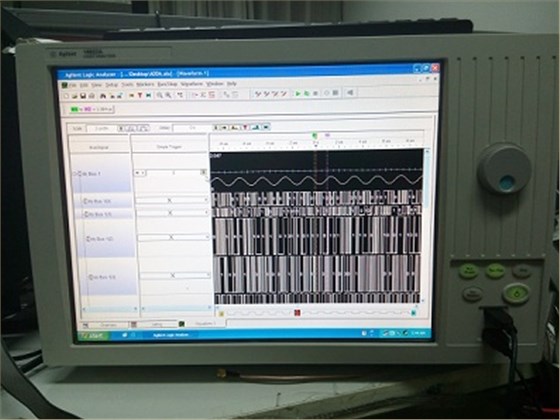

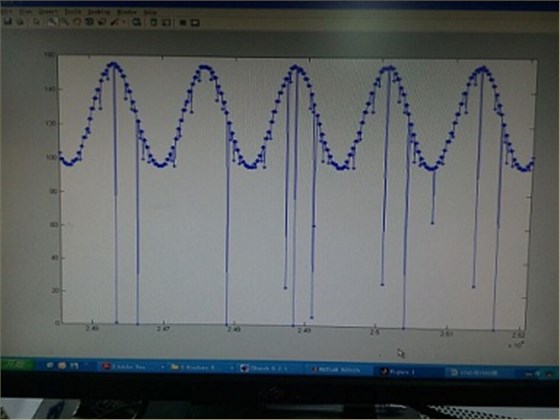

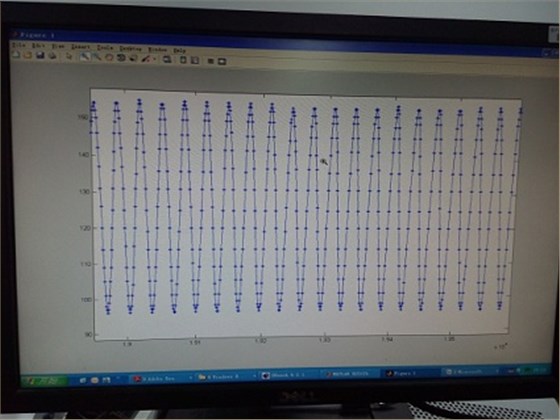

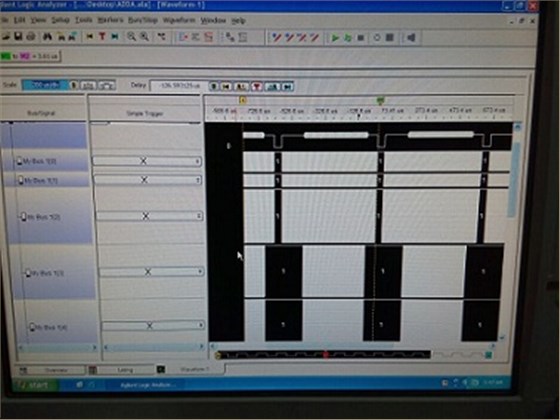

用Agilent 16822A Logic Analyzer测试ADC量化的10bit信号,如下图所示,因为逻辑分析仪有电平判决,ADC 1.8V CMOS电压也可以兼容,而且可以设置采样的边沿可以选择rising edge还是falling edge,再加上逻辑分析仪的电缆线可以做到屏蔽性好、等长等特性。

下图是用逻辑分析仪,直接分析ADC量化的10bit的数据,不经过FPGA处理。

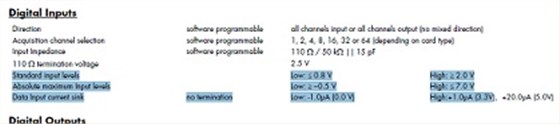

2io level

我们可以从m2i.7011数字IO卡的datasheet中,可以知道,IO卡对于高低电平的判决是高于2.0V当成高电平1来处理,低于0.8V当成低电平0来处理。

The high level ≥2.0V

The low level ≤0.8V

m2i.7011对于高低电平的判决是datasheet写的是3.3V,5V的TTL电平标准。

即使我们把输入阻抗impedance调节成110ohm,电压是2.5V还是不兼容1.8V。

但是采集蓝牙信号的ADC芯片输出的是1.8V的CMOS电平,这样电平不一致将导致IO卡无法预知高低电平的信号,一般高电平对于数字信号来说是1,低电平是0。如果无法正确的预判是1还是0,对于数字IO卡来说,就会采集不到正确的0和1的值。

所以,需要把ADC的数据先进入FPGA,进行电平转换,转换成3.3V的电平,为了和IO卡匹配。转换完之后,需要把FPGA的的管脚引到IO口的插针上,但是引到IO插针上的时候,用Agilent的逻辑分析仪,采集原理和IO卡一样,就是多了电平判决和采样时钟沿的选项,这样可以应对许多种IO信号。m2i.7011卡,电平不可以可选,m4i.77xx是可以选择电平标准的,m2i.7011默认是上升沿采集信号,不能使用下降沿采集信号。

LEADCORE公司的ADC芯片设计比较怪异,因为一般ADC芯片,TI或者ADI的ADC,量化ADC数据adcdata的时候,会有dclk,所谓dclk就是和adcdata一起同步出来的信号,这样时钟和数据都是同步的,但是LEADCORE公司的ADC芯片只有adcdata,没有随路时钟dclk,他们选择的方式是FPGA这边直接给1个16MHz的时钟,16MHz的时钟使用xilinx公司的virtex-5信号DCM,产生同频率,相位分别为0°,90°,180°,270°的16MHz时钟,xilinx virtex-5芯片的DCM产生时钟,报低能产生32MHz的时钟,但是产生16MHz的时钟,拿示波器量确实是16MHz,可能是xilinx的一个bug。

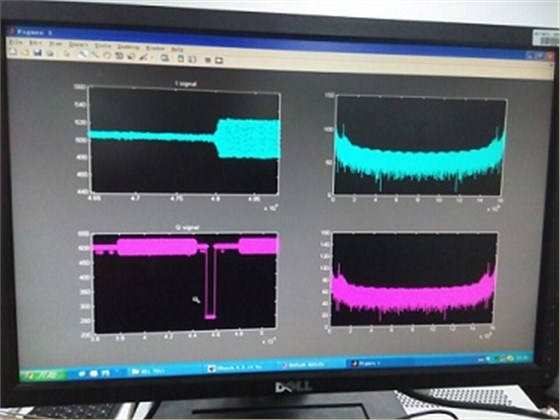

DCM产生的4个时钟里面,有1个或者2个,可以让dclk和adcdata尽量的满足setup time和hold time,保证采集的数据在时序上没有violation。这样就能避免出现下图的现象:

实际测试,发现没有了IO delay的错误,反而多了一个周期性的干扰的毛刺,而且毛刺的位置非常固定。拿Agilent Logic Analyzer测试10bit的IO数据,发现在1个周期的sinus波形里有个周期性的干扰。

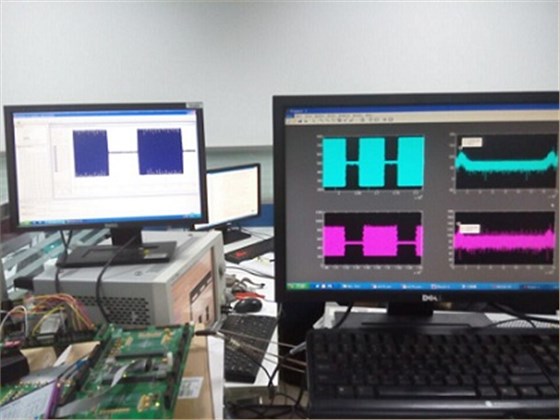

后再拿m2i.7011数字IO卡,测试,采集完存成bin文件,用MATLAB观察,现象和Agilent的逻辑分析仪现象一致。

再仔细观察突变的位置,刚好是512左右,我们再分析10bit的数据1000000000是512,也就是说刚好高位从0到1翻转的过程中突变了,导致1变成0,导致数据突然下跌。

我们知道,对于数字电路来说,10bit的数据,在逻辑里面如果经过D触发器,10bit的数据要发生翻转都在在时钟的上升沿或时钟的下降沿,因为D触发器属于边沿触发器。对于边沿比较敏感。

那10bit的数据,就需要10个D触发器,每个触发器存1bit的值,那如果是由时钟边沿引起的第10bit的数据,周期性的翻转受干扰,那我们就用上面DCM产生的4个相位的时钟,分别试验。

如果4个时钟都是同样的现象,就可以定位是硬件上的问题了。

终,经过试验,发现是ADC芯片引出的IO上有问题,所以更换了IO,重新采集。可以采集到平滑的sinus波形。

3bluetooth signal

使用Agilent基于移动领域的WiMAX矢量信号源MXG,产生蓝牙信号包,蓝牙包里可以叠加噪声。

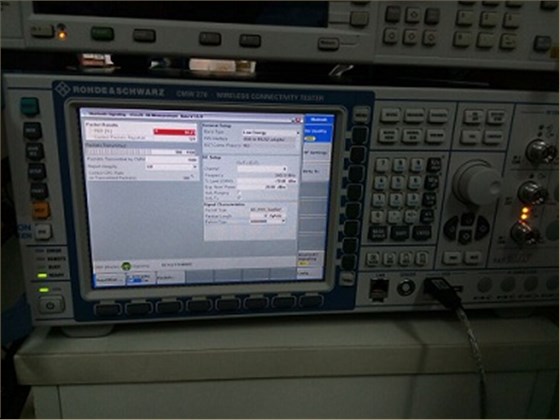

使用Rohde&Schwarz公司的无线通信CMW270,可以统计蓝牙包的误报率。

当把一切环境都搭建好,可以使用m2i.7011采集数字IO信号了,数字IO卡使能的bit数可以从datasheet知道。

8bit、16bit、32bit,因为采集IQ两路总共需要20bit,还需要1bit GND和1bit CLK,所以需要使能32bit的IO,采样时钟选择外时钟16MHz。

下图是使用m2i.7011采集的IQ蓝牙包IO波形。

同样用Agilent的逻辑分析仪看到蓝牙包是一包一包出现的。

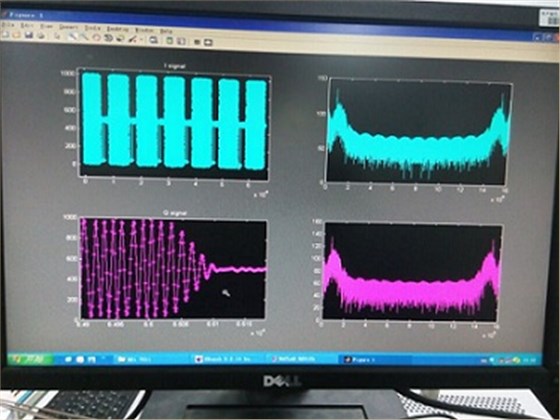

我们使用chipscope抓取蓝牙包,使用MATLAB把采集的32bit的IO数据进行解析,会看到IQ两路的蓝牙包。

蓝牙包根据不同的叠加噪声会有不同的时域表现。

4summary

北京坤驰科技的数字IO卡基于采集的是数字IO信号,每个IO口对应1bit的数据,其功能类似于逻辑分析仪,IO卡的优点在于体积小,可携带,可插与普通电脑或者便携式机的PCIE或PCI插槽使用,接口形式示采集卡是PCI还是PCIE接口。数字IO卡支持可编程,支持多个IO,多可使用64个IO口,相比于Agilent 16822A逻辑分析仪,逻辑分析仪缺点是数字IO口少,只支持16个数字IO口和1个CLK和1个GND,无法满足2路IQ产生的20bit数字信号。

电话咨询

电话咨询 产品中心

产品中心 在线留言

在线留言 关于坤驰

关于坤驰