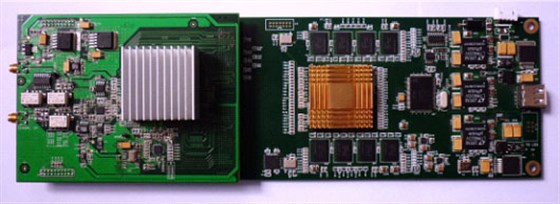

采集系统规格:

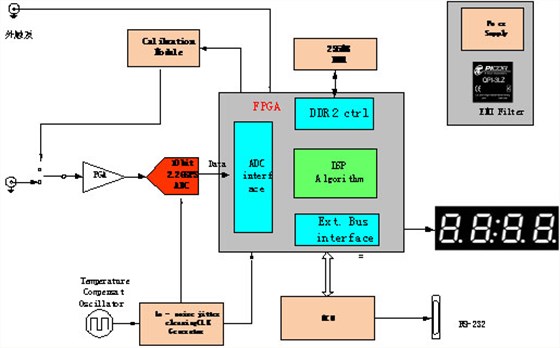

系统采用基于FPGA的采集加数据分析系统,包括如下几个部分:

1.10bit2.2GSPSADC,单通道。采样率可以通过软件设置。

2.低噪声模拟前端,支持+/-5V~+/-200mV信号输入,50Ω阻抗BNC接口。

3.板载256MBDDR2内存。

4.优化的USB2.0传输接口,支持33MB/s的连续传输速率。

5.支持外部触发输入。

6.16个可编程GPIO,可用于系统控制。

7.高稳定度,超低低抖动时钟发生器。

8.低噪声电源设计。

9.板载高精度自适应校准电路及算法。

10.LED显示,指示毛刺数量和状态。

11.毛刺电平输出,兼容TTL电平。

12.FPGA实现实时毛刺检测算法功能。

13.采集数据时间戳功能。

14.用户可通过小键盘或串口进行参数配置和模式选择。

15.宽温设计-20℃~+90℃

16.供电需求,单电源12DC输入,1A电流。

17.外形尺寸:180mmX90mm

系统整体框图如下:

方案描述:

该采集系统主要用于长时间采集1通道脉冲信号:

1.采集脉冲信号,实时检测其脉冲上的毛刺,并判断有无毛刺。

2.对毛刺信号进行计数(通过数码管显示),实时上报毛刺情况(通过IO输出)。

3.保证ADC的SNR以及长时间宽温的工作稳定性。

毛刺信号的检测算法:

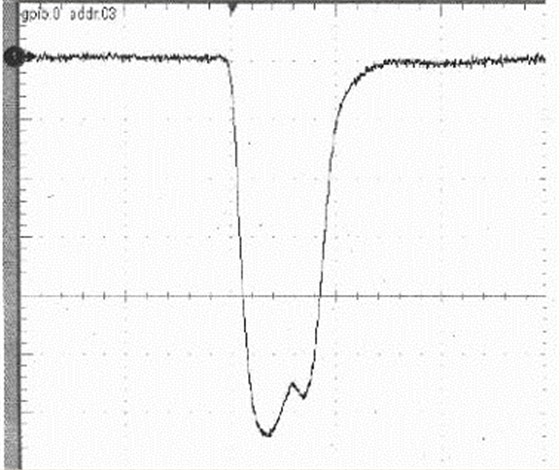

输出的信号如下:

为了准确检测包络信号的毛刺,我们首先检测信号峰值,并判断信号峰值的类型,是真正的峰值,还是毛刺的峰值。通过设置一定门限来区分毛刺和真正的峰值。

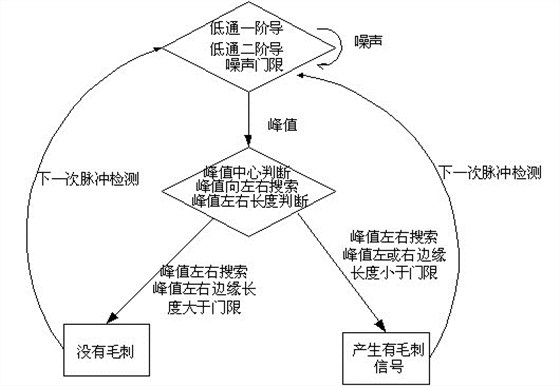

为防止信号噪声的干扰,我们引入低通一阶导和低通二阶导的概念。检测流程如下:

其核心算法判断峰值中心,并同时向左向右(时间前后)进行边缘长度搜索,一单在门限以内还存在另一个峰值,就可以判断毛刺的存在。哪怕俩个峰值相互重合,通过检测峰值边缘长度也能判别叠加在峰值上的毛刺。

同时为了准确的采集,采集系统的信噪比SNR必须得到保证。影响采集精度的主要要素有以下几点:

量化误差、Clockjitter和ADCjitter、数字以及电源干扰

量化精度的提高:

对于量化误差对采集系统的影响,我们在该系统中选用10bit的ADC,理论

Clockjitter的消除:

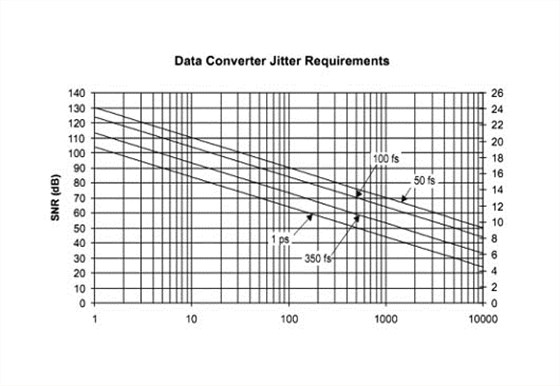

该方案中采用温度补偿晶体TCXO以及业内顶级的JittercleaningCLKGenerator芯片来保证clock的稳定性,Clockjitter的消除以及极低的Phasenoise。

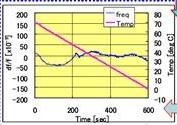

在宽温工作环境下,普通的晶体随着工作温度的变化,晶体的稳定度和频率都会发生改变,为解决该问题,我们在设计中选用epson公司的TCXO,该晶体具有业内领先的温度稳定性,在宽温工作环境下不会超过+/-2ppm,其温度测试性能如下:

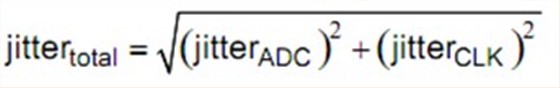

对于时钟芯片的选择,也是基于同样的考虑,集成高精度高稳定的VCO,具有Jittercleaning功能和clkphaseadj功能。通常,jitter由ADC本身的jitter和CLKjitter组成,各自的RMS再组成总jitter的RMS:

总jitter的RMS会在采集系统中产生白噪声,其关系如下:

采集系统的总和

采用本时钟解决方案,其总的clockjitter在系统中完全能做到<1ps。在忽略信号noise,DNL等情况下,fin和clockjitter有如下关系:

系统电源干扰的解决方案:

1.电源抑制(PSR)是采集系统的比较重要的指标,高的PSR能拟制电源上的CML共模噪声,该方案中选用的ADC具有80dB以上的电源拟制比。

2.有效的数字-模拟电源隔离和滤波电路。本方案中采用PICOR的专业有源EMI滤波器,能在电源上产生65dB的共模制比和80dB的差模拟制比,远远高于通用的磁珠等EMI滤波效果。

3.合理的PCB布线和接地

板卡实物图:

电话咨询

电话咨询 产品中心

产品中心 在线留言

在线留言 关于坤驰

关于坤驰