一、概述:

项目背景:

该项目主要用于光脉冲在不同介质中的传输特性不同,来实现对目标的跟踪。

本系统主要应用于水下目标的特征探测。

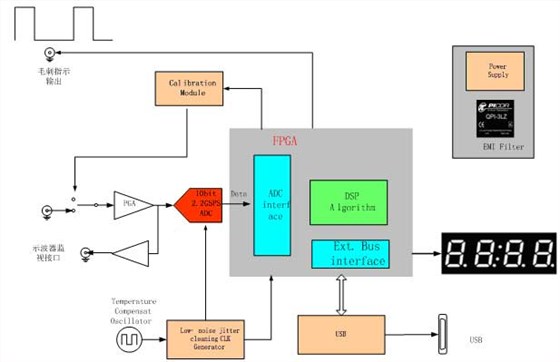

系统框图如下:

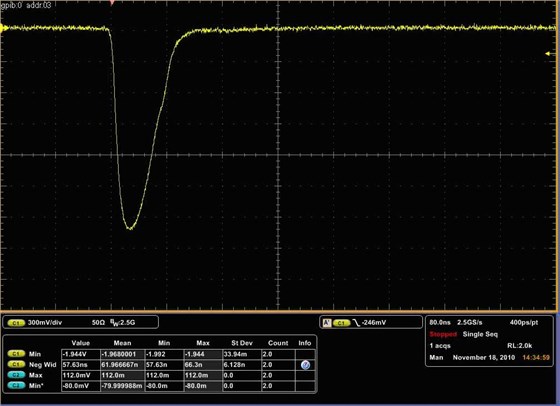

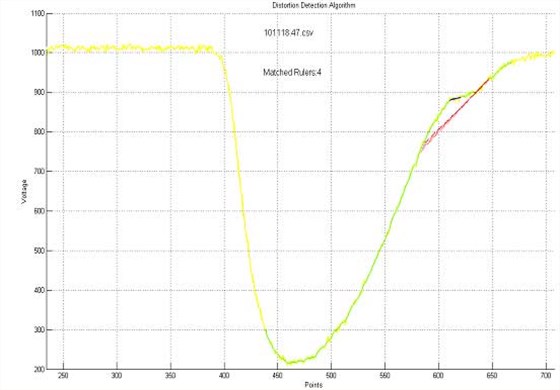

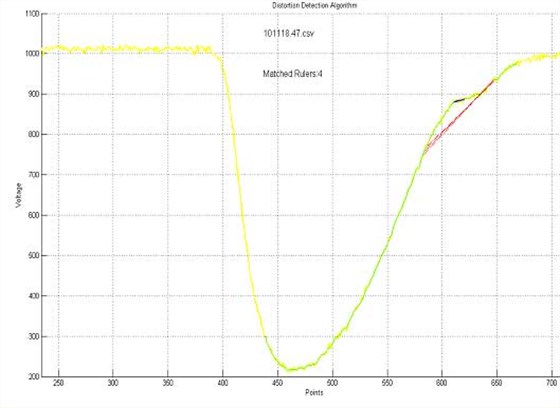

当光电倍增管接收的光为均匀的介质是产生的经典本底信号如下:

本底信号采用2.5Gsps采样,下降时间约40ns。

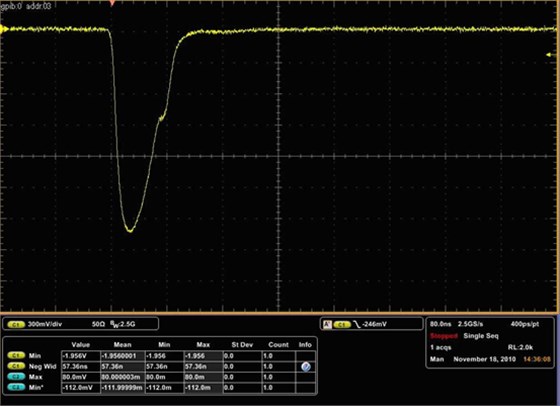

当光电倍增管接收的光为遇到介质中的“气泡”时,将在上图的本底信号的上升沿产生畸变,典型信号如下:

由于气泡的位置和大小不确定,所以会产生不同的畸变大小、形状且畸变的位置也是不固定的。

我们的任务就是需要采集到光电倍增管输出的高速脉冲,通过FPGA实现数字信号实时处理,判别和区分开当前的信号是本底信号还是有畸变的信号,将该信号的特征上传到主机。

我们面临的挑战:

1、光电倍增管输出的脉冲信号非常的窄,且上升时间特别陡峭;这就需要我们采用高速ADC进行采集。

2、脉冲信号为负脉冲,且幅度较小;这就需要特殊设计ADC的前端放大器,采用高速高带宽直流放大器并且增加高稳定度偏置电路。

3、水下环境复杂,有时本底信号和有气泡的信号区别不是很大,这就需要设计更复杂的算法进行更精确的分析和判别;算法复杂程度较大。

4、本底和畸变差别较小本底和畸变差别中等本底和畸变差别较大。

5、由于采用高速采集,采集时钟为2GHz,远高于FPGA所能接收的速度,所以需要采用并行计算的方式来实时处理采集到的信号。

解决方案:

根据实际系统和算法处理精度要求,硬件系统采用如下设计:

1、10bit2GSPSADC,单通道。

2、低噪声模拟前端,支持+/-5V~+/-200mV信号输入,50Ω阻抗BNC接口。

3、板载128MBDDR2内存。

4、16个可编程GPIO,可用于系统控制。

5、高稳定度,超低低抖动时钟发生器。

6、低噪声电源设计。

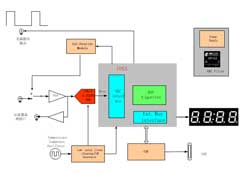

7、LED显示,指示含有畸变信号的数量和状态。

8、FPGA实现实时信号特征检测算法功能。

9、USB2.0接口,用户可以通过USB进行参数配置以及接收计算结果。

10、宽温设计-20℃~+90℃

11、供电需求,单电源12DC输入,1A电流。

12、外形尺寸:220mmX90mm

二、系统整体框图如下:

三、信号的检测算法:

设计思想:我们根据不同的波形曲线进行实时特征统计,提取曲线的特征点,在找到特征点的关键点的性质,来分析有无畸变情况。

目前特征点的条件定为如下几点:

特征点由三部分组成

a.一阶导数的零点

b.二阶导数的零点

c.函数本身的极值点

判决方法为这些特征点的特性变化:

1.计算相邻特征点的方向向量

2.计算相邻向量改变角度值

3.相邻特征点向量方向转变角度阈值,超过该阈值,则认为曲线有可观测到的变动

判决畸变的规则:

若输入序列开始为负值,则找到序列第2个正值(连续2个为正)再开始判断

1.若此后序列值符号变化为正(至少再有1个点为正)->负,则判断存在畸变(曲线出现内凹)

2.满足连续3个点值为正,且数值变化小于中间值的25%,则判断存在畸变(畸变形状近似直线)

3.满足连续5个点值为正,且数值均小于一个阈值K_TH(较小的数),则判断存在畸变(畸变形状近似直线)

4.满足一阶导数存在2个以上的较大峰值(大于平均正值斜率均值1.5倍),且峰值大于两峰之间的斜率均值2倍以上,则存在畸变(曲线部分外凸)

这些规则分别判定有尖的毛刺,有直线变化以及外凸等情况。该算法架构大的好处是可以根据实际情况增加判决规则。

典型数据测试测试结果:

对于典型的畸变信号,顺利检测出畸变量=25。

对于典型的本底信号,畸变量=0。

对于较小的畸变,畸变量=4。

附录:

高速采集卡的挑战

为了准确的采集,采集系统的信噪比SNR必须得到保证。影响采集精度的主要要素有以下几点:

1、量化误差。

2、lClockjitter和ADCjitter。

3、数字以及电源干扰

量化精度的提高:

对于量化误差对采集系统的影响,我们在该系统中选用10bit的ADC,理论

Clockjitter的消除:

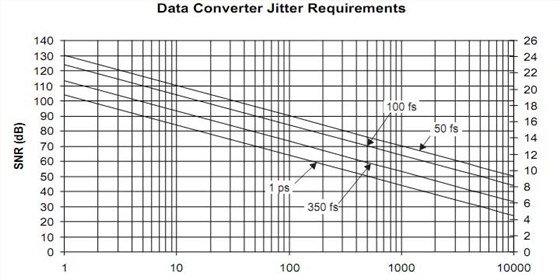

该方案中采用温度补偿晶体TCXO以及业内顶级的JittercleaningCLKGenerator芯片来保证clock的稳定性,Clockjitter的消除以及极低的Phasenoise。

在宽温工作环境下,普通的晶体随着工作温度的变化,晶体的稳定度和频率都会发生改变,为解决该问题,我们选用超低相位噪声的晶体。

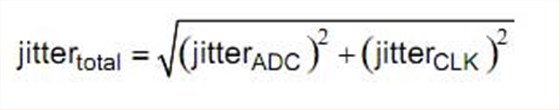

对于时钟芯片的选择,也是基于同样的考虑,集成高精度高稳定的VCO,具有Jittercleaning功能和clkphaseadj功能。通常,jitter由ADC本身的jitter和CLKjitter组成,各自的RMS再组成总jitter的RMS:

总jitter的RMS会在采集系统中产生白噪声,其关系如下:

采集系统的总=

采用本时钟解决方案,其总的clockjitter在系统中完全能做到<1ps。在忽略信号noise,dnl等情况下,fin和clockjitter有如下关系:

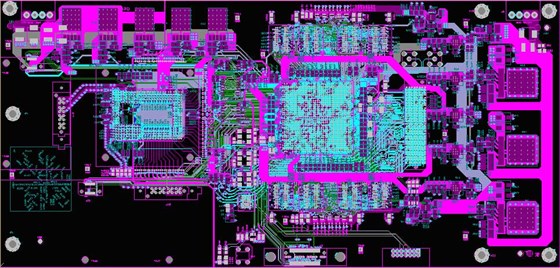

合理的高速数模混合PCB设计,充分论证信号完整性和电源完整性,PCB版图如下:

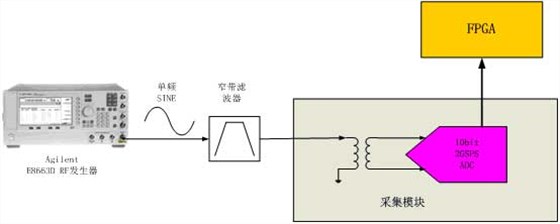

采集测试方案以及ADC芯片性能力指标

1.ADC性能测试

ADC模块的测试:

使用AgilentE8663DRF信号发生器,主要发生单频的sine信号,通过窄带滤波器,保证sine的“纯净”。信号幅度为+/-1V输出,保证ADC输入的满幅度。

信号通过ADC采集后进入PC并存储,通过测试软件进行数据处理。

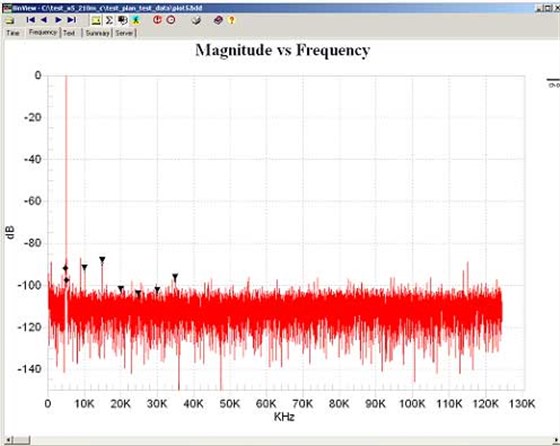

关于ADC采集数据的处理及计算方法:

Data输入可以选取多个点(如4K-16K),同hanningwindow进行卷积,防止矩形窗引起的Gibbs现象。

卷积后的信号进行FFT,得到频谱数据。这是为了测试数据的准确性,可以多采集几次进行谱平均,得到更准确的谱数据。

ADC性能的测试:

我们可以在频谱中找到输入sine的基波信号,以及除去其高次谐波的噪声能量,得到SNR的指标:

SNR=20*log([Fundamental]/SQRT(SUM(SQR([Noise]))))

以及

SFDR=20*log([Fundamental]/[HighestSpurious])

SINAD=20*log([Fundamental]/SQRT(SUM(SQR([Noise+Harmonics]))))

ENOB=(SINAD–1.76)/6.02

根据如上测试方法,本系统的采集性能达到如下性能指标:

Fs=2Gsps

Fin=500MHz

SNR:42dBc

ENOB:7bit

THD:45dBc

SFDR:48dBc

电话咨询

电话咨询 产品中心

产品中心 在线留言

在线留言 关于坤驰

关于坤驰