以往要想以14bit分辨率、2GS/s的速度检测微弱脉冲信号,是无法实现的,现在北京坤驰科技有限公司的ADQ14系列数据采集卡结合行业领先、自身专有的降低噪声技术开发了相关的高级时域固件(ATD),实现了以上快速、高分辨率的微弱脉冲信号检测功能。该脉冲数据采集系统包含以下核心内容:

·用于脉冲数据线性识别的滤波函数

·用于噪声非线性抑制的阈值运算函数

·通过重复测量计算波形平均抑制噪声

1,工作原理

高级时域固件的应用目的是加强用于脉冲测量的高速数据采集卡的信噪比。固件包含一个基线调节器、三个噪声抑制级别、线性滤波、非线性阈值、能够降低噪声的重复测量波形平均功能。

ADQ14系列高速数据采集卡的每个通道都配置有一个高级时域固件(ATD)单元,在相同的波形尺寸和累积数量设置下,同步工作。每通道的阈值是独立设置的。

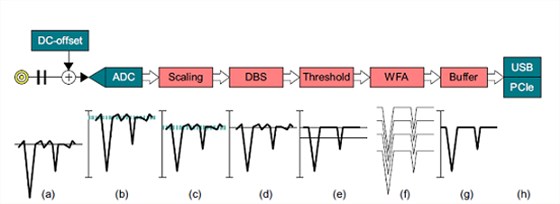

每通道高级时域固件的原理图如下:

图1

上图的相关信号解释及设置函数见下表:

2,模拟输入

如图1(a),输入模拟信号为单极性,这意味着信号相对于一个DC值基线和一个信号脉冲构建的。信号的DC值不必为0,一些DC耦合的高速数据采集卡,将使得输入信号的直流电平高于0点,如果需要,AC耦合版本,可以移动输入DC电压值。

一个模拟的DC偏置加到信号中,可实现ADC的对称输入范围充分使用。这将使信号基线接近信号范围的上限或下限。峰值波形能覆盖所有信号范围。直流偏置有效的加倍了单极信号的分辨率。如图1(b).直流偏置(DC-offset)电压由软件控制,控制范围为电压上限到下限,但好留有10%的范围,以适应信号过冲。

3,零电位调准和信号缩放

当为了获取理想电压范围使用直流偏置(DC-offset),基线接近信号一端,如果需要,可使用数字化增益和偏置调整模块来缩放信号。

4,数字基线稳定器,DBS

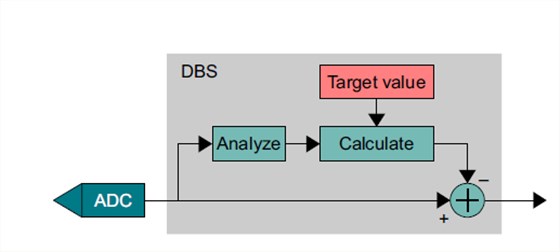

对于常见的直接信号分析,模拟的直流电平(DC-level)是准确的,然而,为得到非线性阈值操作的佳性能,基线应该锁定为一个确定值。本处由数字基线稳定器(DBS)实现,其配置在A/D转换器之后。DBS是SP devices的一项专利技术,通过分析数据、找到和调整基线为22位精度的目标值。如图2.

目标值由使用者设定,好接近模拟增益(DC-offset),如果应用了DC-offset这一功能。DBS应用了模糊识别的方法进行数据处理,DBS是一直激活的,其不断的监视和跟随基线变化,并矫正基线为时不变值。

图2

5,高级阈值设置

5.1 概述

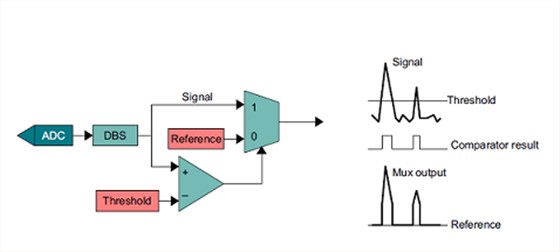

阈值功能基于以下几个基本模型(依据单极性脉冲的极性),如图3.

·对于采集系统的正脉冲,采样低于阈值(设置的参考值)

·对于采集系统的负电压,采样高于阈值(设置的参考值)

处理结果为,与阈值相等信号和低于阈值的信号被视为噪声被移除。

图3 正脉冲的基本阈值操作

5.2 利用滤波器的线性噪声抑制

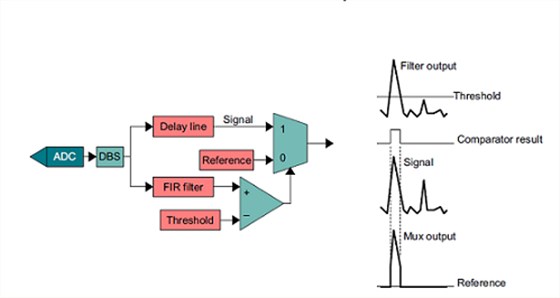

当脉冲具有可以与本底噪声分离的性质时,滤波功能就可以用来加强信号特性,之后性噪比会提高,阈值精度也会提高。滤波器通常为形状相关的,使用滤波或相关功能时,脉冲由多个样本复现出来。

例如:低通滤波器将辨别噪声的高频部分,因此降低噪声的峰值幅度。

例如:对弱脉冲的形状已经初步了解时,使用滤波器相关到其形状,以放大这类有用形状,压缩其他形状,也就是压缩噪声。

注意到,滤波器仅对选择的处理过程起作用,输出数据并不滤波。

5.3 应用阈值

原理如图4所示,噪声抑制的非线性部分,原理是使得认为是信号得部分为大幅度,噪声部分为小幅度。

在脉冲能够识别的位置,阈值应用到滤波信号,高于阈值的原始信号极其位置会保存下来。注意到阈值应用到滤波信号,因此原始非滤波信号数据为输出数据,这是为了保留原始信号波形形状,图中的延迟线(delay line)用来匹配分支运行时间。

没有脉冲的位置被寄存器R的存储值代替,寄存器R存储值与DBS的目标值相同。

图4 数据流。滤波信号用于选择采样位置,原始信号用于结果输出

5.4 准确度

阈值精度由DBS的准确度决定,22bits。通常,DBS将依据22bits时的测量误差调整基线值为14位整数,阈值和参考值为相同数据格式时,没有舍入误差。

6 ,波形平均

6.1 累加数据字

波形平均是利用累加器将波形相加后求平均,每个波形的个样本加到其他波形的个样本,每个波形样本都有相同的长度,每个数据字的尺寸为32bits,因此,输入14bits数据高有效位(MSB)对齐到16bits字。有16位的可用空间用于存储附加信息。这意味着硬盘数据溢出之前,可存入2^16=65536个波形数据。波形平均功能包括针对波形数目的除法,然而,这个除法不能适用于FPGA,需由用户软件操作完成。

6.2 累加矢量长度

波形平均使用板上DRAM作为累加器。波形数可以很大,多5Msamples。

6.3触发

每个波形都由触发启动,所有的采样触发都可选为波形触发。系统波形平均更好的利用了重复测量功能,触发可以是来自于与外部触发源的外部触发也可以是内部触发。通常,脉冲形状可以分析,触发电平用于多次触发重复脉冲。

每个波形结束后的空载时间为20ns,为上一次采样结束到系统接收新的触发的时间间隔。

7, 数据读出到主机

由于数据读出到主机的速度小于数据采集的速度,板上必须有一个额外的缓冲空间在波形数据发送到主机之前存储波形。经由累加器的波形平均后,PC数据率的需求是降低很多的。但当后一个波形被累加后,一段时间内,累加器为数据读出封锁并不再接收新的波形。ADQ14通过引入一个外加的缓冲区(buffer),在数据读出之前保存结果,同时不封锁累加器。一个新的累加过程将于20ns后启动。

8 ,仿真结果

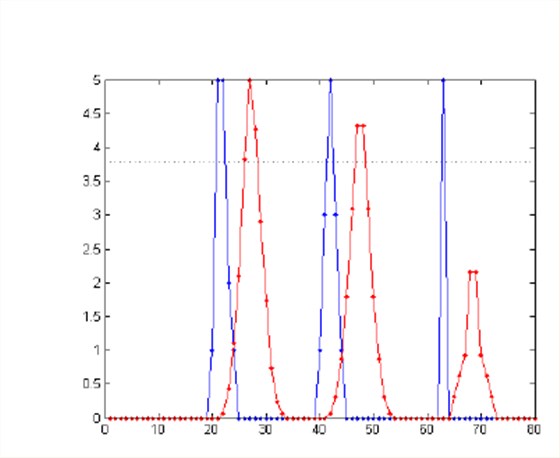

图5中显示了相对于同一采样时钟不同相位的脉冲信号,蓝色信号带有尖峰噪声。红色信号为滤波后的结果。这里的关键是信号脉冲波形大于一个采样宽度,噪声波形小于一个采样宽度,这是典型的高斯噪声。

图5

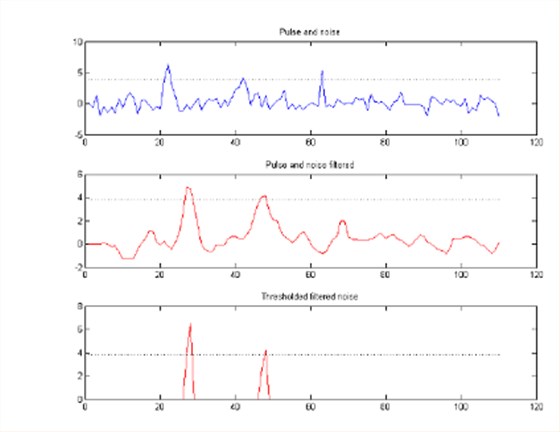

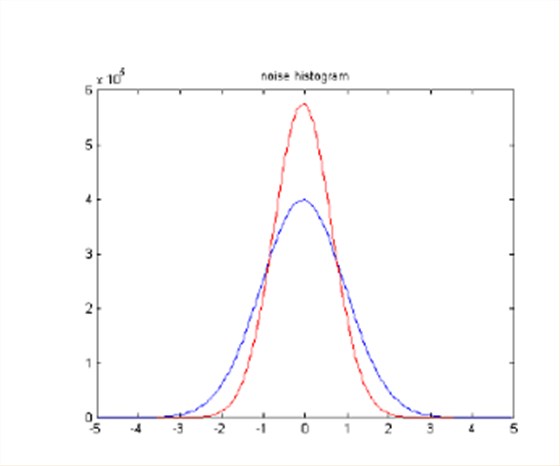

图6显示了来自于图5的两列脉冲和高斯尖峰噪声,蓝色曲线为滤波前,红色为滤波后。底部红色曲线来自基于阈值的原始信号滤波后的阈值滤波噪声。图7为滤波前后的噪声直方图,滤波后,噪声幅度降低。

图6 滤波前后的两列脉冲和随机噪声尖峰

图7 滤波前后的噪声直方图

9, 并行采样处理

FPGA 的数据率仅为250MHz,因此,高速数据采集时,采样操作必须为并行处理,这会给一些尺寸设置带来了约束条件,例如,匹配信号路径到滤波器的延迟时间设置为8个步长,为了微调各个操作分支的时间,滤波器峰值的位置可以移动一个采样长度。

电话咨询

电话咨询 产品中心

产品中心 在线留言

在线留言 关于坤驰

关于坤驰