1.概述

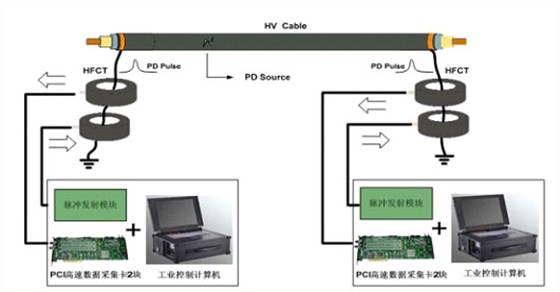

该系统主要应用于局放传感器的信号采集及分析,实现在线和离线局放监测。

1.1采集系统规格:

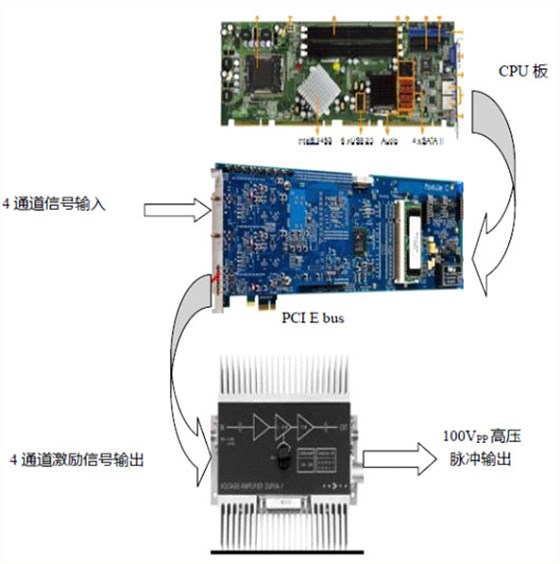

系统基于PCIExpress总线结构,包括如下几个部分:

1.1.14通道8bit500Msps同步采集,标准PCIe全长卡尺寸;

1.1.24个高速IO,产生激励脉冲输出。

1.1.3外置脉冲放大器,输出100Vpp的激励短脉冲。

1.1.4基于PCIExpressx8总线的工控机。

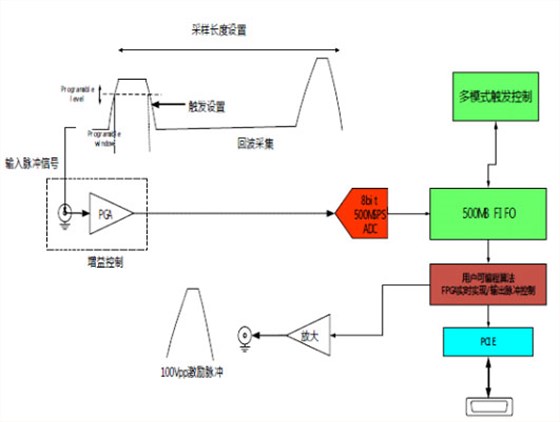

1.2采集系统实现框图:

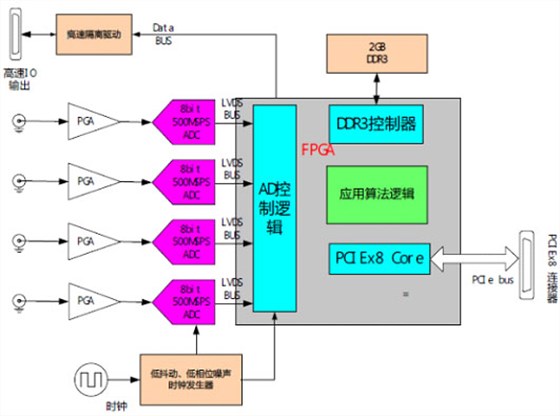

1.3采集系统原理框图:

1.4数据采集卡特性:

1.4.14通道8bit500MSPS同步采集。

1.4.24通道程控增益放大器,增益倍数0-100倍调整,满幅度输出1Vpp。

1.4.3输入通道DC耦合,50欧姆输入阻抗。

1.4.4模拟输入带宽DC-120MHz/-3dB。

1.4.5输入端口过压保护,允许200W/20us浪涌功率输入。

1.4.62GB本地缓存,保证每次触发,每通道有0.5S的采集时间。

1.4.7支持PCIEx8接口,连续数据传输率1000MB/s。

1.4.8低抖动、低相噪时钟发生器。

1.4.9可以多块卡组成多通道同步工做模式。

1.5系统工作模式:

1.5.1触发设置:可以根据输入脉冲的幅度和宽度设置触发判决条件。

1.5.2输入放大倍数可以通过软件设置。

1.5.3输出脉冲相对于触发事件时间可以设置,小单位为2ns。

1.5.4出脉冲和触发事件条件随机延迟不超过4个采样点,及8ns。

1.5.5触发后,采集长度可以设置,大每通道可以采集500M个点。

1.5.6可以回传长度为500M个点的原始波形供计算机软件分析。

1.6脉冲发生:

1.6.1性能指标:

1.6.1.1电源:AC90V-260V

1.6.1.2输出功率:瞬时20KW

1.6.1.3平均功率:小于300W

1.6.1.4输出脉冲幅值:100V,500V,1000V三档可选,在50?时

1.6.1.5输出脉冲宽度:100ns-10us

1.6.1.6触发单元脉冲延迟:375ns+/-5%

1.6.1.7脉冲发生器脉冲延迟:750ns+/-5%

1.6.1.8可设置输出脉冲延迟:25ms

1.6.1.9触发门槛范围(上限):5mV~150mV

1.6.1.10触发门槛范围(上限):100mV~1000mV

1.6.1.11触发极性:正脉冲或负脉冲

1.6.1.12输入带宽:50MHz

1.6.1.13输入抑制:当没有输入时,将每100秒发出脉冲消除反射脉冲重新触发装置

1.6.1.14自由运行模式:在固定间隔内连续产生脉冲

1.6.1.15自由运行模式时间间隔:1毫秒,1秒,1分钟

1.6.1.16输入/输出保护:采用气体放电管保护

1.6.1.17输入输出连接:BNC接口

1.6.1.18电源:电池供电,10小时连续供电

1.6.2通信方式:

1.6.2.1采用串行通信方式:

通过一个控制口和一根地线串行控制脉冲电源

1.6.2.2可接受电平:3.3V5V或10V(认可信号:低电平小于1V高电平大于2V)

1.6.2.3约定控制信号三个8位数据段,每个位(bit)1US,高电平为1低电平为0。

停止位为1位起始位为1位。

个8位段发送:255(11111111)

用来表示启始同步。每收到这个信号,接收器将接收并认可接下来的三个命令段。

第二个8位段:

表示脉冲宽度。基数0.1us(100ns)比如发20(00010100)代表脉冲宽度为2us。

大认可100(01100100)即10us。

第三个8位段:

表示电压档位选择。1(00000001)代表100V2(00000010)代表500V3(00000011)代表1000V

2.系统配套软件:

系统软件包括应用软件,二次开发API函数,以及FPGA开发环境三部分。

2.1应用软件

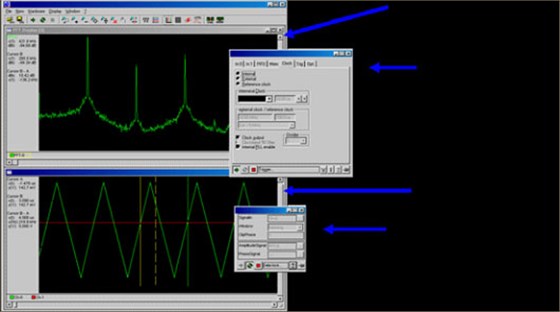

具有虚拟示波器功能,方便设置硬件,读取/保存数据以及波形显示/频谱分析功能。

其功能和界面如下所示:

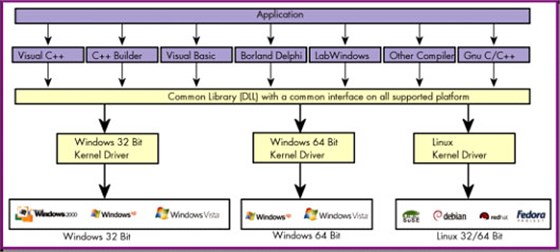

2.2二次开发API函数:

我们提供丰富的接口函数和系统主要功能的例程,支持C/C++,labview以及Matlab环境下的二次程序开发。

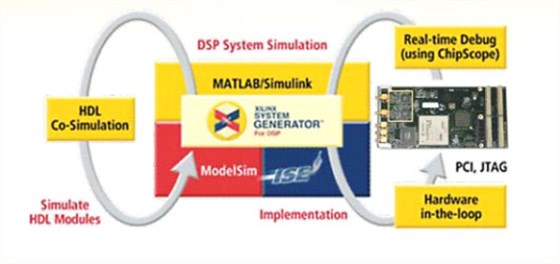

2.3FPGA开发环境:

我们提供采集模块的全套FPGA开发工程,全部基于VerilogHDL或VHDL开发环境。用户逻辑只需要在目前已经建立好的工程中加入自己的RTL代码即可。

同时提供Xilinx的systemgenerator同matlab/simulink接口工程和实例。

电话咨询

电话咨询 产品中心

产品中心 在线留言

在线留言 关于坤驰

关于坤驰