在当今的工业领域,系统电路板布局已成为设计本身的一个组成部分。因此,设计工程师必须了解影响高速信号链设计性能的机制。在高速模拟信号链设计中,印刷电路板(PCB)布局布线需要考虑许多选项,有些选项比其它选项更重要,有些选项则取决于应用。终的答案各不相同,但在所有情况下,设计工程师都应尽量消除佳做法的误差,而不要过分计较布局布线的每一个细节。本应用笔记提供的信息对设计工程师的下一个高速设计项目会有所帮助。

1、裸露焊盘

裸露焊盘(EPAD)有时会被忽视,但它对充分发挥信号链的性能以及器件充分散热非常重要。裸露焊盘是目前大多数器件下方的焊盘。它是一个重要的连接,芯片的所有内部接地都是通过它连接到器件下方的中心点。不知您是否注意到,目前许多转换器和放大器中缺少接地引脚,原因就在于裸露焊盘。

关键是将此引脚妥善固定(即焊接)至PCB,实现牢靠的电气和热连接。如果此连接不牢固,就会发生混乱,换言之,设计可能无效。

2、实现佳连接

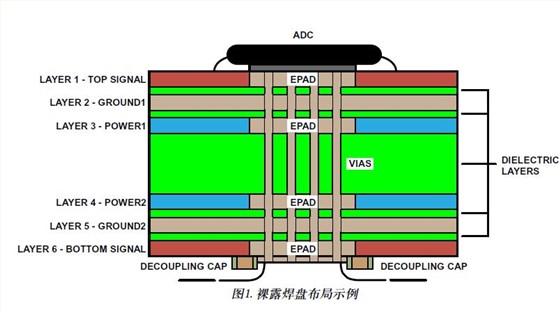

利用裸露焊盘实现佳电气和热连接有三个步骤。首先,在可能的情况下,应在各PCB层上复制裸露焊盘,这样做的目的是为了与所有接地和接地层形成密集的热连接,从而快速散热。此步骤与高功耗器件及具有高通道数的应用相关。在电气方面,这将为所有接地层提供良好的等电位连接。甚至可以在底层复制裸露焊盘(见图1),它可以用作去耦散热接地点和安装底侧散热器的地方。

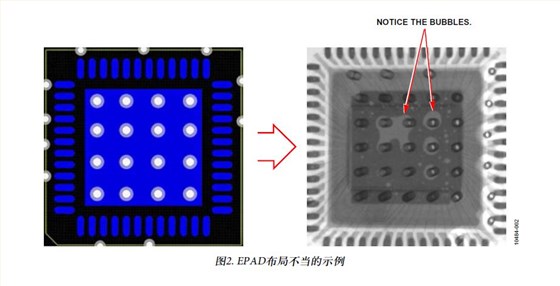

其次,将裸露焊盘分割成多个相同的部分,如同棋盘。在打开的裸露焊盘上使用丝网交叉格栅,或使用阻焊层。此步骤可以确保器件与PCB之间的稳固连接。在回流焊组装过程中,无法决定焊膏如何流动并终连接器件与PCB。连接可能存在,但分布不均。可能只得到一个连接,并且连接很小,或者更糟糕,位于拐角处。将裸露焊盘分割为较小的部分可以确保各个区域都有一个连接点,实现更牢靠、均匀连接的裸露焊盘(见图2和图3)。

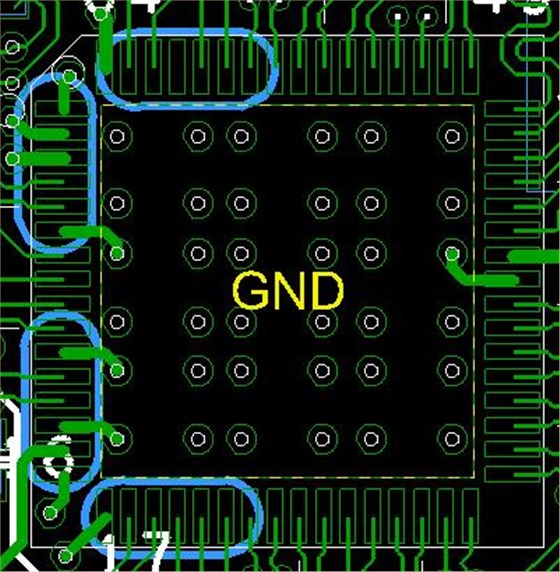

后,应当确保各部分都有过孔连接到地。各区域通常都很大,足以放置多个过孔。组装之前,务必用焊膏或环氧树脂填充每个过孔,这一步非常重要,可以确保裸露焊盘焊膏不会回流到这些过孔空洞中,影响正确连接。后,应当确保各部分都有过孔连接到地。各区域通常都很大,足以放置多个过孔。组装之前,务必用焊膏或环氧树脂填充每个过孔,这一步非常重要,可以确保裸露焊盘焊膏不会回流到这些过孔空洞中,影响正确连接。

3、去耦和层电容

有时工程师会忽略使用去耦的目的,仅仅在电路板上分散大小不同的许多电容,使较低阻抗电源连接到地。但问题依旧:需要多少电容?许多相关文献表明,必须使用大小不同的许多电容来降低功率传输系统(PDS)的阻抗,但这并不完全正确。相反,仅需选择正确大小和正确种类的电容就能降低PDS阻抗。

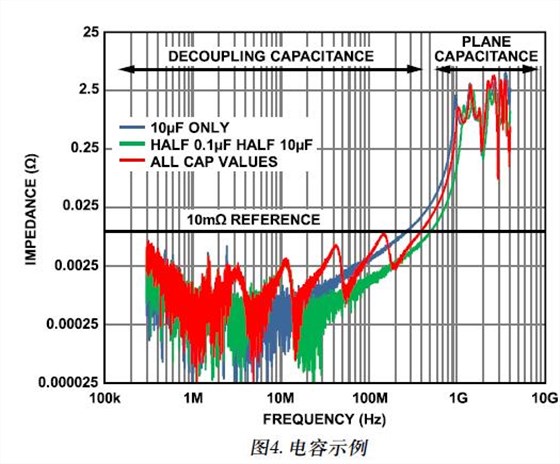

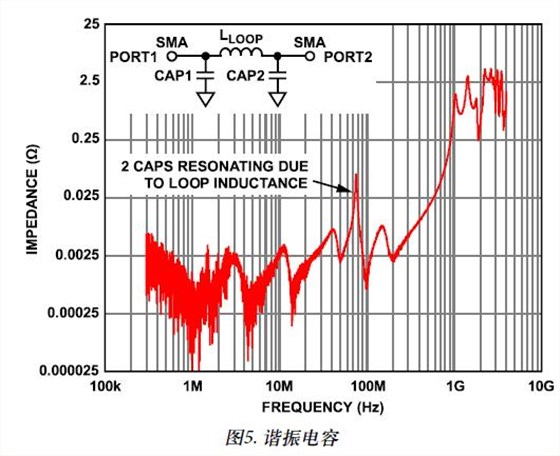

例如,考虑设计一个10mΩ参考层,如图4所示。如红色曲线所示,系统电路板上使用许多不同值的电容,0.001μF、0.01μF、0.1μF等等。这当然可以降低500MHz频率范围内的阻抗,但是,请看绿色曲线,同样的设计仅使用0.1μF和10μF电容。这证明,如果使用正确的电容,则不需要如此多的电容。这也有助于节省空间和物料(BOM)成本。注意,并非所有电容“生而平等”,即使同一供应商,工艺、尺寸和样式也有差别。如果未使用正确的电容,不论是多个电容还是几个不同类型,都会给PDS带来反作用。结果可能是形成电感环路。电容放置不当或者使用不同工艺和型号的电容(因而对系统内的频率做出不同响应),彼此之间可能会发生谐振(见图5)。

4、PDS的高频层电容

要设计出合格的PDS,需要使用各种电容(见图4)。PCB上使用的典型电容值只能将直流或接近直流频率至约500MHz范围的阻抗降低。高于500MHz频率时,电容取决于PCB形成的内部电容。注意,电源层和接地层紧密叠置会有帮助。

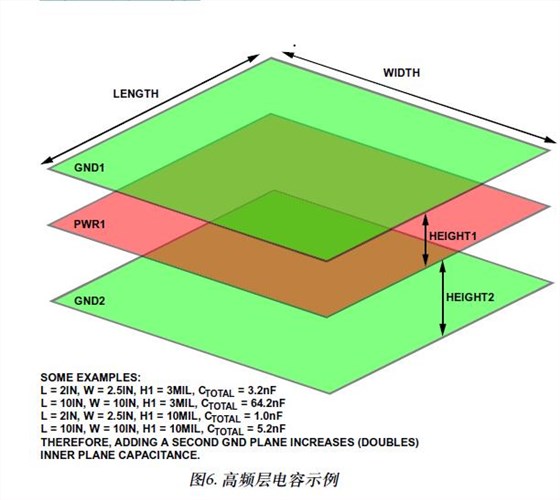

应当设计一个支持较大层电容的PCB层叠结构。例如,六层堆叠可能包含顶部信号层、接地层、电源层、第二电源层、第二接地层和底部信号层。规定接地层和电源层在层叠结构中彼此靠近,这两层间距为2到4密尔,形成一个固有高频层电容。此电容的大优点是它是免费的,只需在PCB制造笔记中注明。如果必须分割电源层,同一层上有多个VDD电源轨,则应使用尽可能大的电源层。不要留下空洞,同时应注意敏感电路。这将使该VDD层的电容大。

如果设计允许存在额外的层(上例中,从六层变为八层),则应将两个额外的接地层放在和第二电源层之间。在核心间距同样为2到3密尔的情况下,此时层叠结构的固有电容将加倍(示例见图6)。与添加更多分立高频电容以在高频时保持低阻抗相比,此结构更易于设计。

PDS的任务是将响应电源电流需求而产生的电压纹波降至低,这点很重要但常被忽略。所有电路都需要电流,有些电路需求量较大,有些电路则需要以较快的速率提供电流。采用充分去耦的低阻抗电源层或接地层以及良好的PCB层叠,有助于将因电路的电流需求而产生的电压纹波降至低。例如,根据所用的去耦策略,如果系统设计的开关电流为1A,PDS的阻抗为10m_,则大电压纹波为10mV。计算很简单:V=IR。凭借完美的PCB堆叠,可覆盖高频范围,同时在电源层起始入口点和高功率或浪涌电流器件周围使用传统去耦,可覆盖低频范围(<500MHz)。这可确保PDS阻抗在整个频率范围内均低。没有必要各处都配置电容;电容正对着每个IC放置会破坏许多制造规则。如果需要这种严厉的措施,则说明电路存在其它问题。

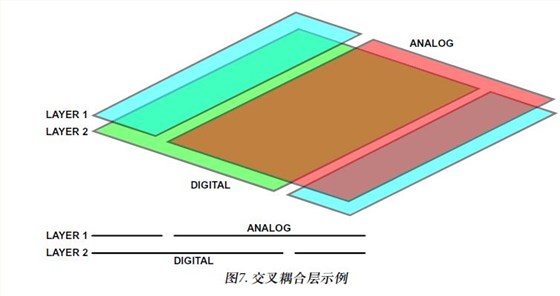

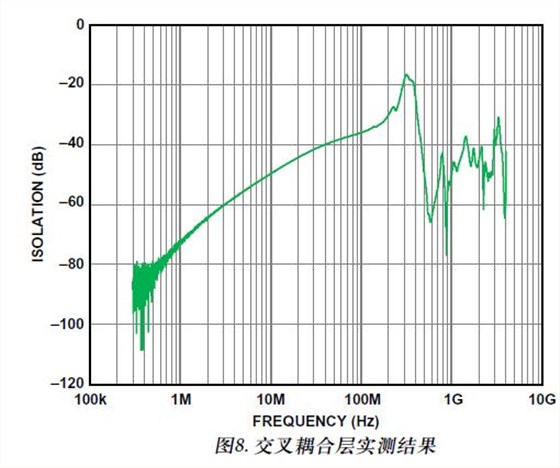

这常常被忽略,因为高噪声层是在另一层——在敏感的模拟层下方。然而,一个简单的实验就可以证明事实并非如此。以某一层面为例,在任一层注入信号。接着连接另一层,将该相邻层交叉耦合至频谱分析仪。耦合到相邻层的信号量如图8所示。即使间距40密尔,某种意义上它仍是电容,因此在某些频率下仍会耦合信号至相邻层。

图8显示了这样的一个例子。举例来说,假设一个层面上的高噪声数字层具有高速开关的1V信号。这意味着,另一层将看到1mV的耦合(约60dB隔离)。对具有2-Vp-p满量程摆幅的12位ADC,这是2LSB的耦合。对于特定的系统这可能不成问题,但应注意,如果系统的灵敏度提升两位,从12位增至14位,此耦合的灵敏度只会提高四倍,即8LSB。

忽略此类型的交叉层耦合可能使系统失效,或者削弱设计。必须注意,两层之间存在的耦合可能超出想象。在目标频谱内发现噪声杂散耦合时应注意这一点。有时布局决定了非预期信号或层应交叉耦合至不同层。同样,调试敏感系统时应注意这一点。该问题可能出现在下面一层。

5、分离接地

模拟信号链设计人员常提出的问题是:使用ADC时是否应将接地层分为AGND和DGND接地层?简单回答是:视情况而定。详细回答则是:通常不分离。为什么不呢?因为在大多数情况下,盲目分离接地层只会增加返回路径的电感,它所带来的坏处大于好处。从公式V=L(di/dt)可以看出,随着电感增加,电压噪声会提高。随着电感增加,设计人员一直努力压低的PDS阻抗也会增加。随着提高ADC采样速率的需求继续增长,降低开关电流(di/dt)的方式却很有限。因此,除非需要分离接地层,否则请保持这些接地连接。

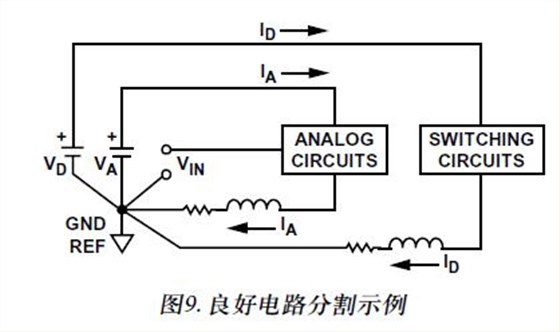

关键是电路分割要合理,这样就不必分离接地层,如图9所示。注意,如果布局允许您将电路保持在各自区域内,便不需要分离接地层。如此分割可提供星型接地,从而将返回电流局限在特定电路部分。

如,受尺寸限制的影响,电路板无法实现良好的布局分割时,就需要分离接地层。这可能是为了符合传统设计要求或尺寸,必须将脏乱的总线电源或高噪声数字电路放在某些区域。这种情况下,分离接地层是实现良好性能的关键。然而,为使整体设计有效,必须在电路板的某个地方通过一个电桥或连接点将这些接地层连在一起。因此,应将连接点均匀地分布在分离的接地层上。终,PCB上往往会有一个连接点成为返回电流通过而不会导致性能降低或强行将返回电流耦合至敏感电路的佳位置。如果此连接点位于转换器、其附近或下方,则不需要分离接地。

为了我们共同的目标“做专业的高速数据采集厂商”而共同努力!

关于坤驰科技:

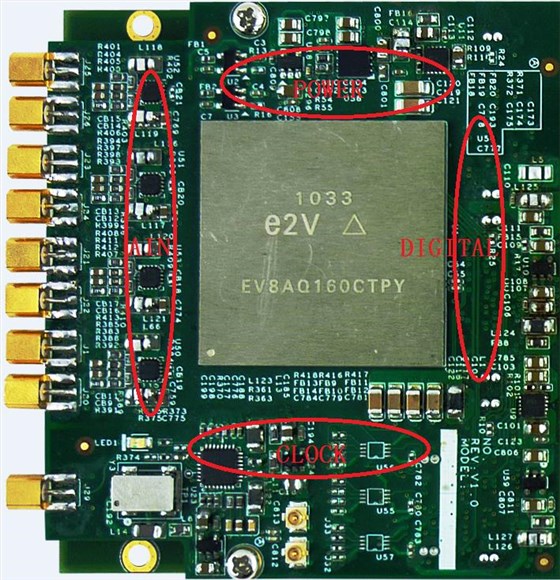

坤驰科技是专注于高速数据采集与信号处理、高速数据存储与记录的高科技公司。坤驰科技为用户提供成熟的标准高速数据采集产品与技术,也可为用户提供定制化的高速信号采集解决方案。目前坤驰科技服务过的研究所、科研单位已达近百家。高速数据采集产品线涵盖PCIExpress、cPCI、PXIe、VPX、USB等总线,包含高速AD、DA平台、FPGA、DSP处理平台,SATA/SSD、Flash存储平台等。

全国咨询电话:400-000-4026

公司官方网站:http://www.queentest.cn

官方微博:http://e.weibo.com/queentest

官方微信:queentest或扫描:

电话咨询

电话咨询 产品中心

产品中心 在线留言

在线留言 关于坤驰

关于坤驰