前言:

随着计算机技术发展,计算机总线速率、处理能力与存储技术得到了快速发展。就存储技术而言相比于五年前,现在不论是传输速率,存储速度与存储容量均有了不同数量级的变化。如现在的PCIe

Express总线可以实现3GB/s (Gen2.0, X8)以上,或6GB/s(Gen3.0,

X8)以上的传输速率;而SATA磁盘容量也可以轻易实现动辄几T,多动几十T的规模。

在高速数据采集领域(一般指的雷达、卫星、无线电、光电、激光等高频物理信号),因试验、监测及装备的需要,对于原始信号的长时间捕捉与存储需求也日益增强。做为实现这些需求的手段,一般搭建一套高速数据采集存储系统是比较常规的方式。做为商用级的采集存储供应商,一般会基于不同应用场景提供了不同的数据采集存储方案。下面列出了常见的几种不同的存储系统:

1、基于PCIe总线计算机采集存储系统:

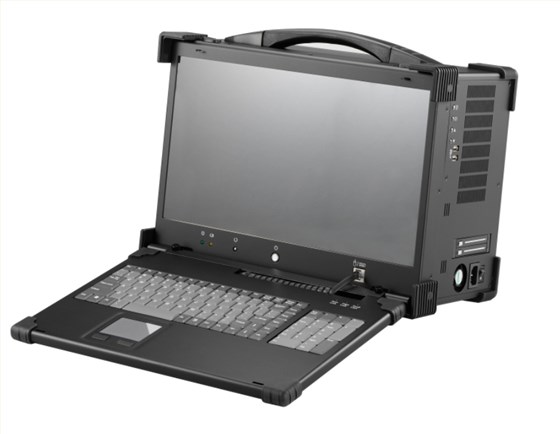

这种系统一般采用PCIe高速数据采集卡做为高速AD转换的入口,高频模拟电信号经高速数据采集卡转换成数字信号后经PCIeX8总线,将数字信号传送至计算机。它的系统的中心是一款仔细挑选的性能卓越的基础计算机,它可以配备有8或

16个驱动器托架和6个PCIe插槽的超微4U塔式机, 并拥有2.4 GHz四核处理器,板载图形处理器,8 GBRAM,专门用于系统安装的256

GB固态硬盘,Windows7操作系统等配置。机箱上自带的865W电源采用风扇静音冷却配置。

根据现场应用需求,并不是服务器型的计算机是唯一选择,便携式计算机搭建成采集存储系统也是可行的。

当为适应超大容量的需求,可以采取采集系统与存储系统分离的方式,存储系统采用专门的塔式服务器陈列列架构。采集单元可以通过万兆光纤口进行数据传输。

坤驰科技提供的QTS采集存储系统,可以通过搭配不同的QT11XX系列板卡和配置不同的计算机存储速率和容量,以适配不同客户需求。QT11XX采集卡的采样率可以从80MS/s到5GS/s,通过设置不同的采样模式,在计算机可以承载的存储带宽内,可以实现连续流盘和长时间记录的目的。

这种系统的核心架构为:PCIe高速数据采集卡、高性能计算机、RAID控制卡、磁盘阵列等。

坤驰科技提供了API函数可以供用户二次开发使用,也提供了图形化界面Qt capturelab进行直接的操作控制。

2,VPX架构的SATA采集存储系统:

对于军用、恶劣环境及外场等应用场合,桌面计算机形态的系统相对不太适合。而基于vpx总线的高速采集存储系统可以规避普通计算机的一些不足,特别是抗震性方面的局限。vpx先天的优势,如高密度接插件,欧卡规格,牢固安装的高可靠导轨等,为在振动等场合(如机载,车载)提供了合适的选择。

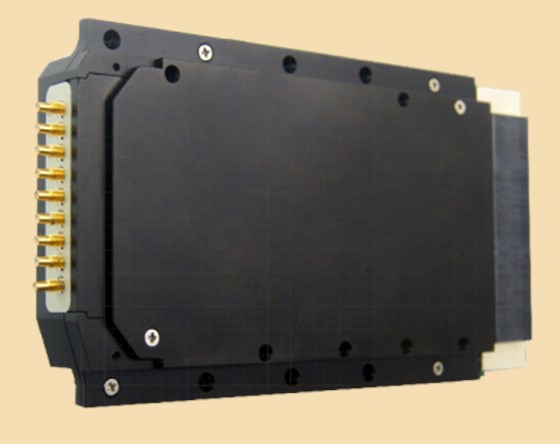

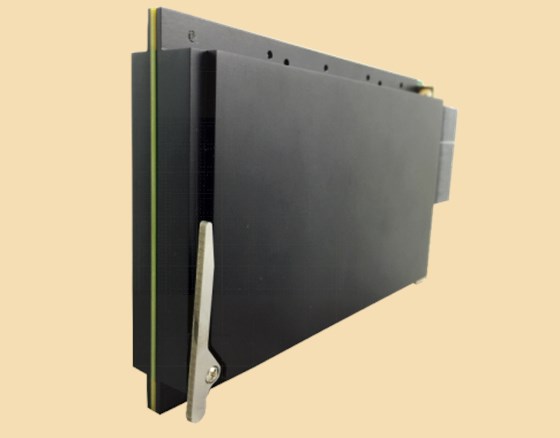

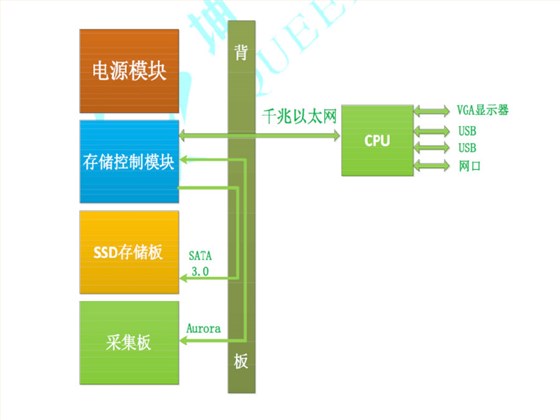

VPX采集存储系统的主要架构一般为:VPX高速采集板,VPX FPGA SATA控制板,VPX 磁盘板(一般选用SSD固态硬盘)及VPX机箱平台等,如下图:

分别形态如下:

高速AD板 FPGA SATA控制板 磁盘存储板

FPGA SATA控制板实现sata的协议解析与sata磁盘的控制,文件系统的构架等。

RTM板:

系统框图为:

3,嵌入式采集存储系统

某些应用场合除了对于采集存储系统要求坚固,可靠,小巧外,他对计算机的依赖比较低。那么一种嵌入式的采集记录仪器也应运而生。它采用自定义的总线结构,FPGA

SATA控制与存储单元集成在一起,而外部信号接口采用fmc的方式做为灵活适配的部件,如用于雷达采集的AD转换板,用于图像采集的mameralink板,用于光纤采集的光纤采集板等。

这种采集记录仪的产品定位为类似于一个黑匣子,可以启动记录,用户可以不必关注它的工作状态,到时直接读取数据即可。

除此,它具备这样的主要特点:

1)超便携式:超便携式数字存储装置是一种通用的海量数据实时记录与存储装置,可以为产品的多种数据提供记录、存储、下载,读写访问等功能。该装置完成客户要求的光纤接口的数据记录与回放,装置主要完成光纤数据记录、回放;同时具有数据查询、检索、提取、预览等对数据管理功能;可通过控制台操作控制;

2)全嵌入式架构:

采集记录过程无OS参与,全FPGA数据采集和直接写入高速SSD盘。架构简洁,数据流程短,可靠性高;光纤数字存储装置可以单台使用,也可以多台集群使用,应对客户需求的全套配置(两台装置集群)和半套配置(单台单独使用)。

3) 高性能:

高速SATA3 6Gbs数据写入协议,成熟的并发写入架构,单盘稳定持续写入可以达到400MB/s以上,单台装置装有至多8块盘,性能不低于3.2GB/s,单台装置支持容量1T、2T、4T、8T、16T,大可支持32T。

4) 数据安全性:

先进的metadata数据管理机制,全部数据文件分块记录,确保后续记录过程中发生意外不影响前面已经记录的数据完整性,以及海量文件检索的可靠性;

5) 易用性:

针对不同应用在上位机更改系统配置,支持友好的用户界面。

总结:

上述介绍是用在科研及装备领域的常见的几种采集存储系统,当然形式不止于上述几种。这些系统根据自身的特点,可以分别应用在实验室、车载、机载、野外等场合。它们可以现实卫星中频、雷达、无线通讯、光纤数字信号、图像信号的记录。

更多信息了解,欢迎访问坤驰科技,获取更多资讯:www.queentest.com; 电话:400-000-4026。

电话咨询

电话咨询 产品中心

产品中心 在线留言

在线留言 关于坤驰

关于坤驰