cPCI/cPCIExpress接收/发送系统

接收/发送系统规格:

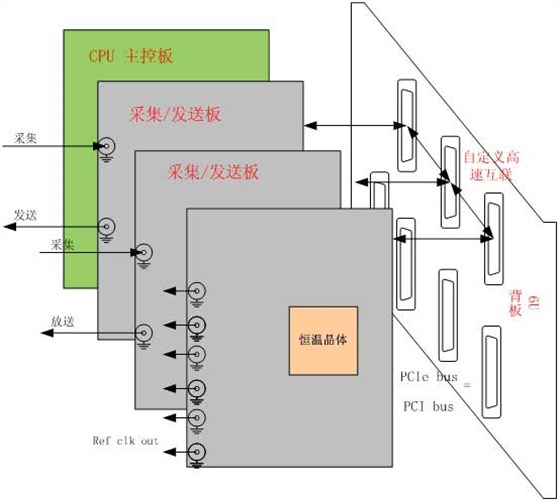

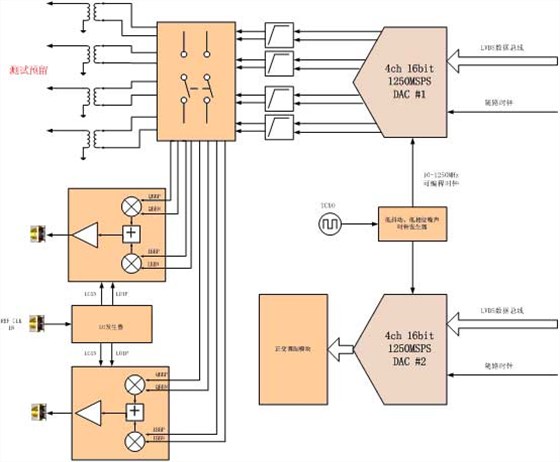

系统采用6U标准的cPCI/cPCIExpress架构,包括如下几个部分:

1.4通道14bit250MSPS采集模块,采用TI的ADS42B49双通道ADC,部署两块该芯片。

2.8通道16bit1250MSPSDAC模块,采用TI的DAC34H84芯片,部署两块该芯片。

3.4通道正交调制模块,采用ADL5385,RF频率范围30MHz-2.2GHz,板载高性能LO发生器。

4.FPGA采用XilinxXC5VLX220TFPGA。

5.板载512MB64位宽DDR2存储器连接到FPGA。

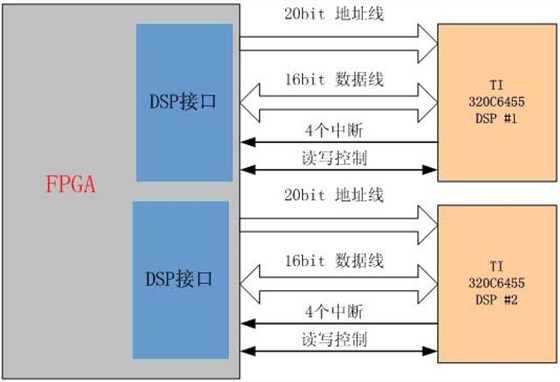

6.两块TI320C6455DSP,分别具有独立的DDR2外存储器和flash芯片。

7.同时支持66MHz32bitPCI总线和PCIEx4总线。

8.外置超低相噪恒温晶体模块,产生LO输入参考时钟。

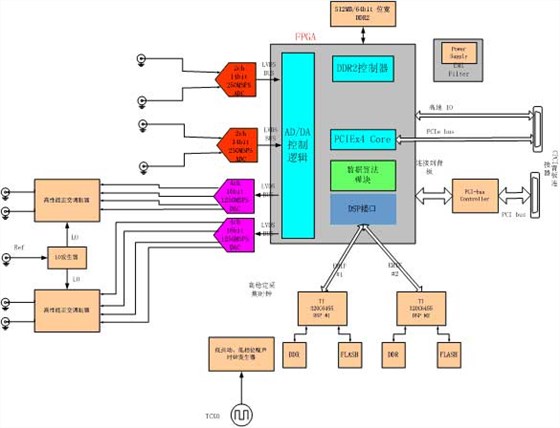

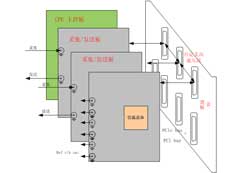

系统实现框图如下:

该接收/发送以及CPU系统的组成模块如下图所示:

由于同时具有PCI总线和PCIE总线以,该系统可以方便的CPU控制板和大容量存储板进行连接,组成更灵活的系统。

采集/发送系统:

采集回放卡包括如下特性:

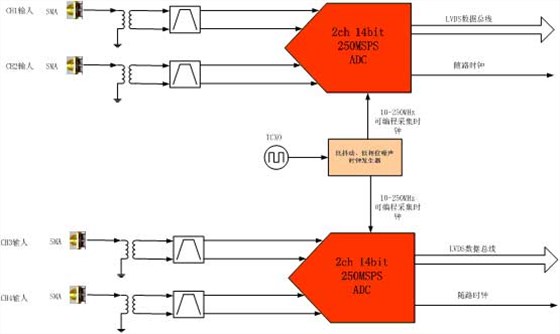

1.2通道14bit250MSPS采集。50欧姆,AC耦合,输入幅度2Vpp,700MHz带宽。

ADC采用TIADS42B49双通道ADC:

信号由SMA接口输入,经过变压器藕合变成差分信号;滤波器为可配置:直通、低通或带通,5阶贝塞尔或巴特沃兹。ADC所有输出数据和随路时钟均连接到FPGA。采集时钟通过高性能时钟发生器产生,采集频率可在10MHz-250MHz范围内编程。

2.4通道16bit1250MSPSDAC,TI的DAC34H84芯片,正交调制器采用ADL5385。

DAC输出采用1:4变压器藕合,预留测试端口,50欧姆负载下高输出1Vpp电压。低通滤波器带宽可以配置。DAC的采集时钟通过高性能时钟发生器产生,采集频率可在10MHz-1250MHz范围内编程。

3.512MB本地缓存。

4.支持PCIEx4接口。

5.支持PCI66M32bit接口

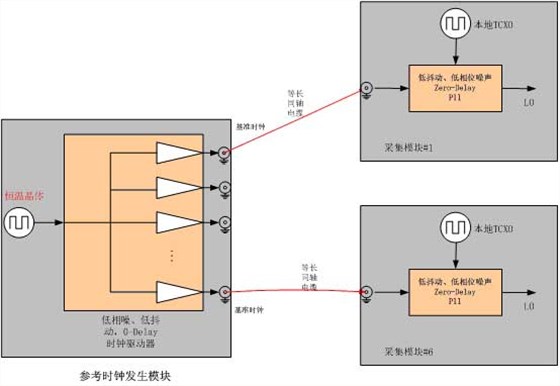

6.低抖动、低相噪时钟发生器。

7.支持8对raidIO高速互联接口,直接将数据通过背板传输到存储控制卡。

8.可以多块卡组成多通道同步工做模式。

9.DSP同FPGA采用EMIF总线连接,连接关系如下:

系统参考时钟发生模块:

本地采用高性能恒温集体,通过驱动器同时输出6-8个参考时钟输出。每个模块采用zerodelayPLL,通过输入参考时钟产生本地的LO给调制器。

采集回放模块性能指标的保障:

对于采集回放模块性能指标,主要保障系统的信噪比大化。通过以下三方面来实现:

1、高精度的采集回放芯片。采集回放模块均采用TI的14bitADC和16bitDAC。支持较高噪声拟制比和采集精度,保障采集精度优于信号本身的量化精度。

2、高稳定,低噪声的电源系统。

3、低抖动以及低噪声的采集时钟放生系统。采用有源温度补偿VCXO,analogdevice的时钟管理芯片,保证了采集系统的高稳定度和低抖动。

关于采集/回放的性能测试:

采集回放系统性能测试方案分为两部分:

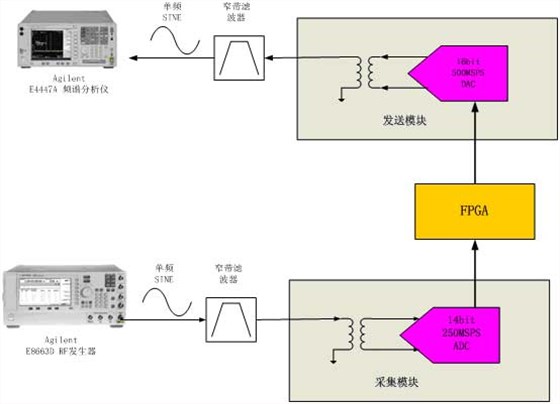

1.测试采集/回放系统本身的性能,如信噪比SNR,THD以及ENOB等测试项目。其测试方法如下:

ADC模块的测试:

使用AgilentE8663DRF信号发生器,主要发生单频的sine信号,通过窄带滤波器,保证sine的“纯净”。信号幅度为+/-1V输出,保证ADC输入的满幅度。

信号通过ADC采集后进入PC并存储,通过测试软件进行数据处理。

关于ADC采集数据的处理及计算方法:

Data输入可以选取2048个点,同hanningwindow进行卷积,防止矩形窗引起的Gibbs现象。

卷积后的信号进行FFT,得到频谱数据。这是为了测试数据的准确性,可以多采集几次进行谱平均,得到更准确的谱数据。

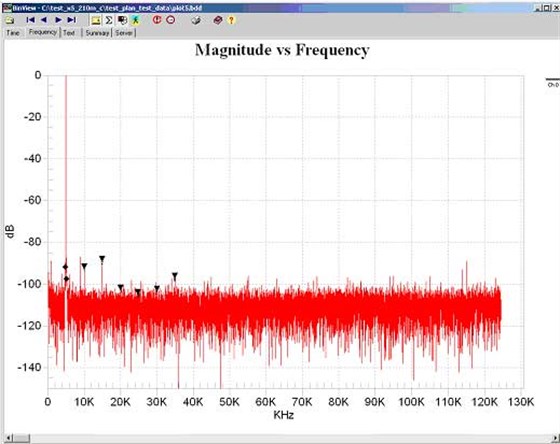

上图为14bitADC在250Msps采样率下采集单频信号的频谱。

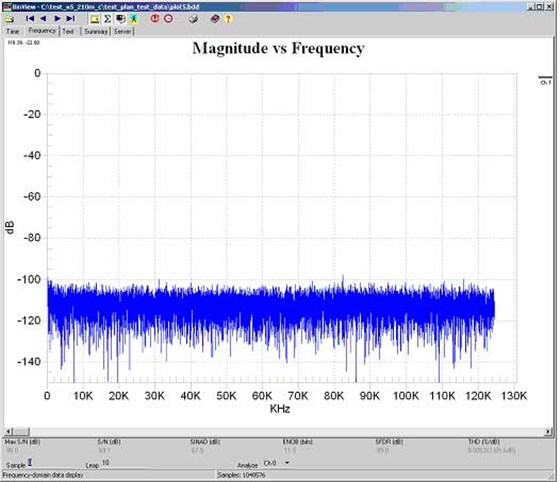

上图为ADC输入底噪声频谱。

DAC的性能测试

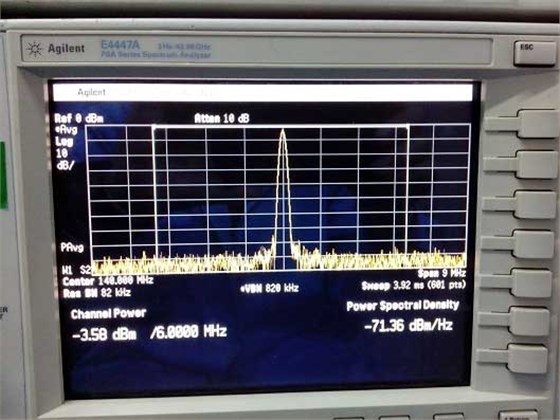

DAC在220MHz时钟下(采用mixfreg算法,相当于110MHz时钟DAC工作在1.25Fs,第二来奎斯特区域)产生140MHz中频的测试结果:

噪声密度在-90dBm。

采集板卡参考外观图如下:

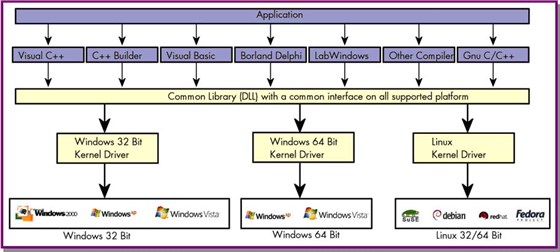

系统配套软件:

系统软件包括应用软件,二次开发API函数,以及FPGA开发环境三部分。

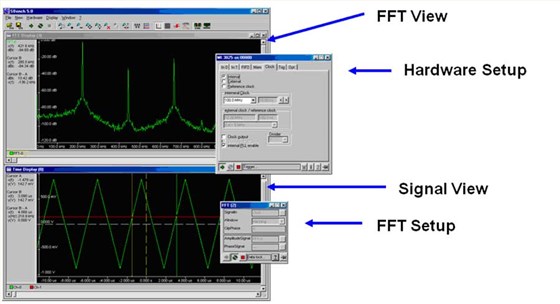

1.应用软件:具有虚拟示波器功能,方便设置硬件,读取/保存数据以及波形显示/频谱分析功能。

其功能和界面如下所示:

2.二次开发API函数:

我们提供丰富的接口函数和系统主要功能的例程,支持C/C++,labview以及Matlab环境下的二次程序开发。

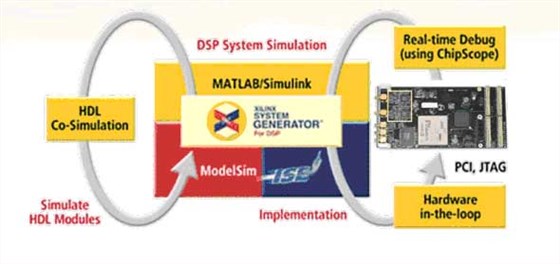

3.FPGA开发环境:

采集模块具备基于VerilogHDL或VHDL的FPGA开发环境。用户逻辑只需要在目前已经建立好的工程中加入自己的RTL代码即可。

同时提供Xilinx的systemgenerator同matlab/simulink接口工程和实例。

电话咨询

电话咨询 产品中心

产品中心 在线留言

在线留言 关于坤驰

关于坤驰