ADC芯片性能测试逻辑和软件平台

ADC芯片性能测试逻辑和软件平台

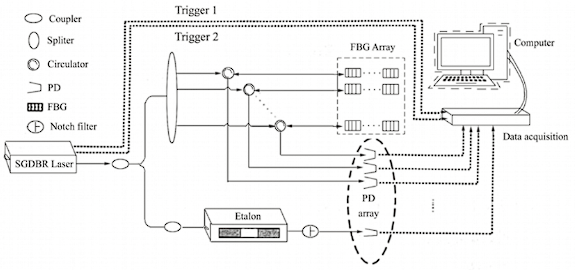

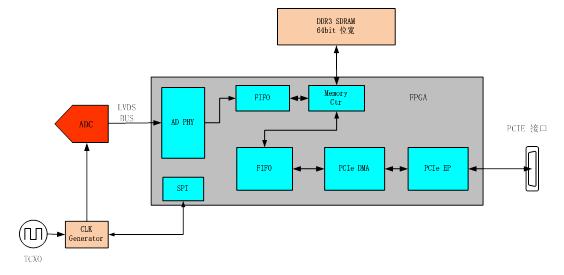

一、系统描述

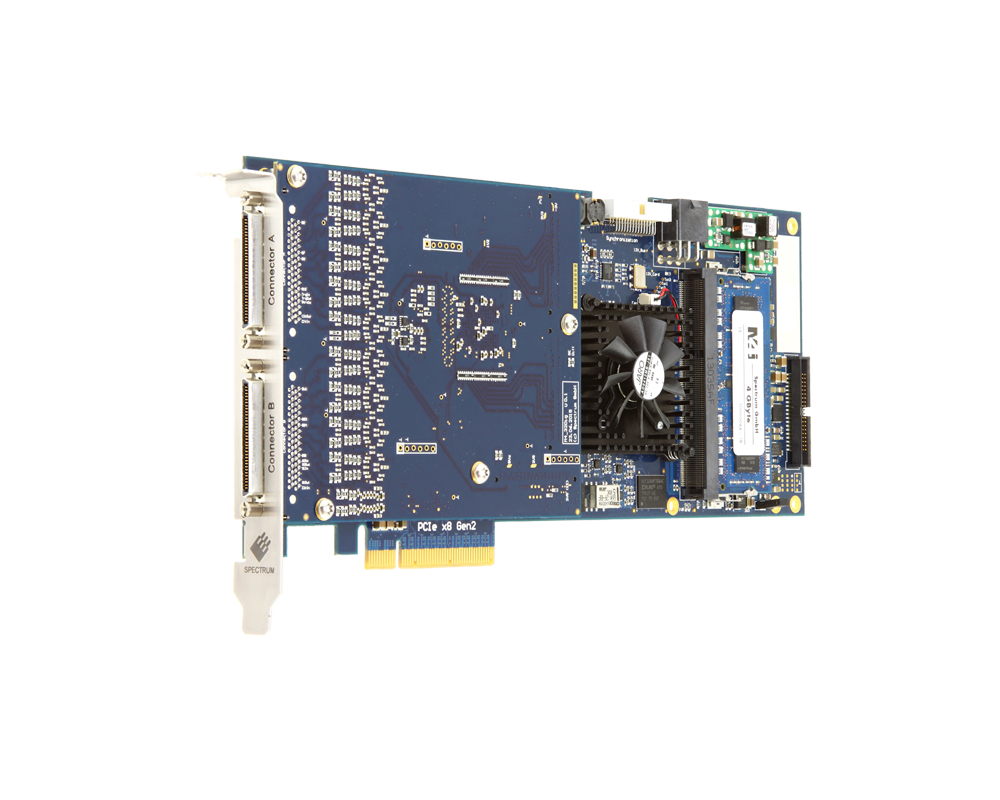

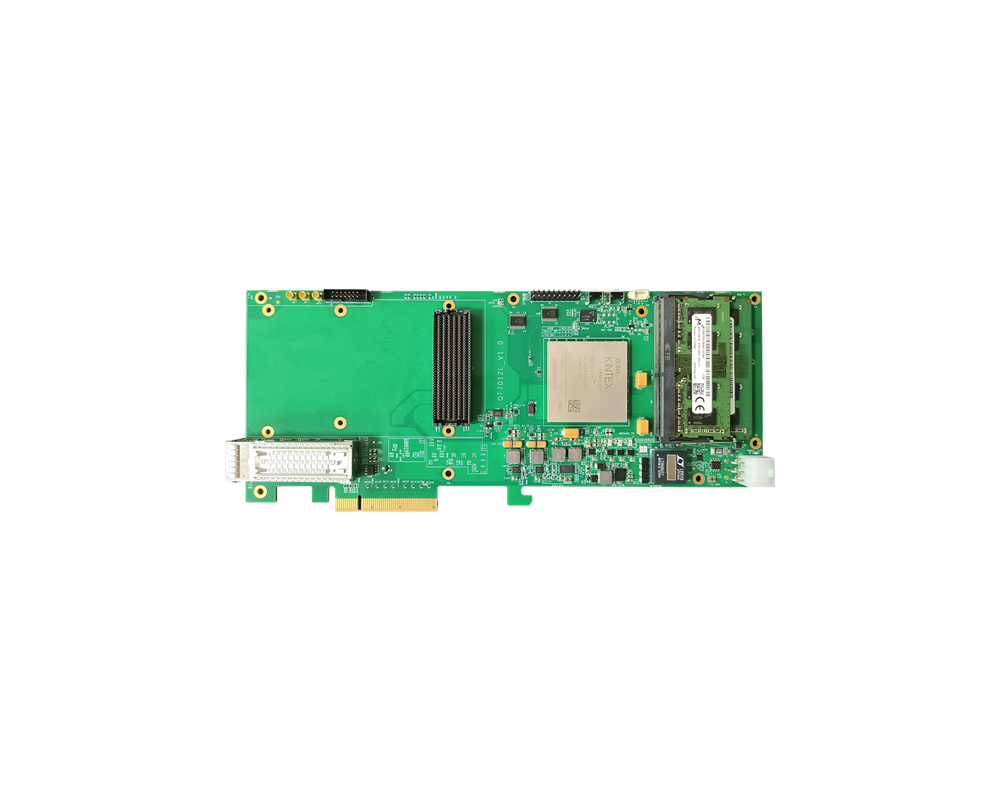

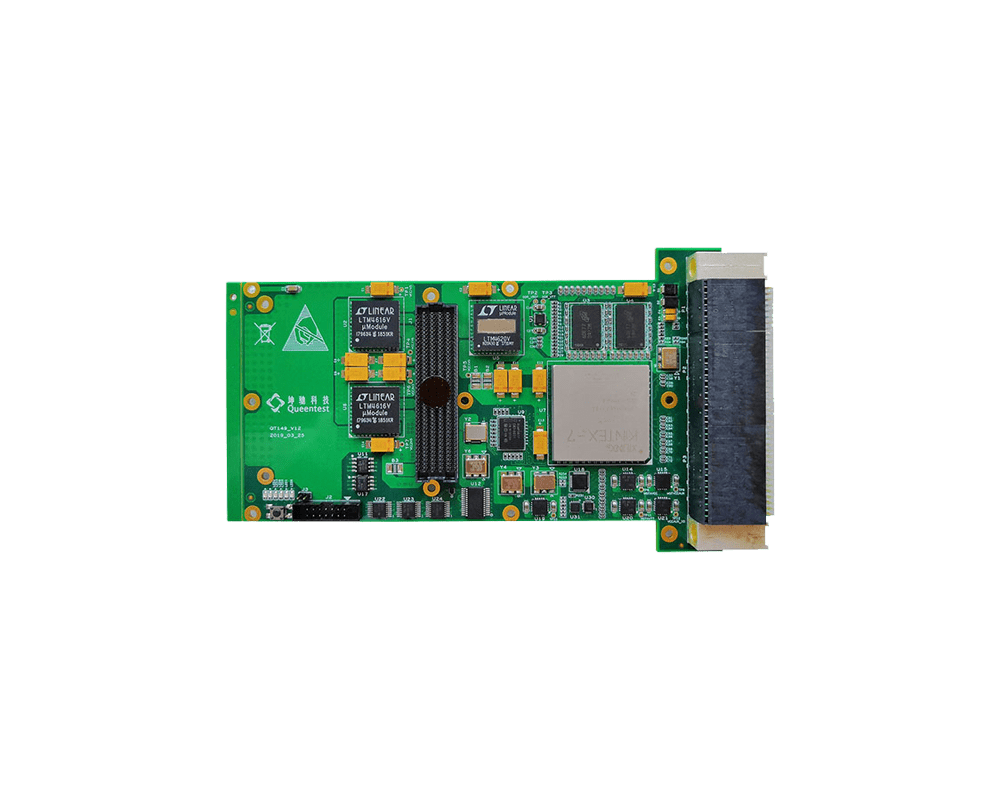

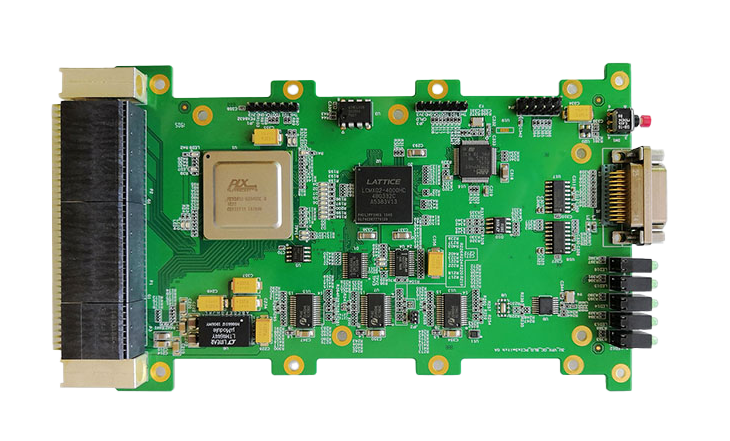

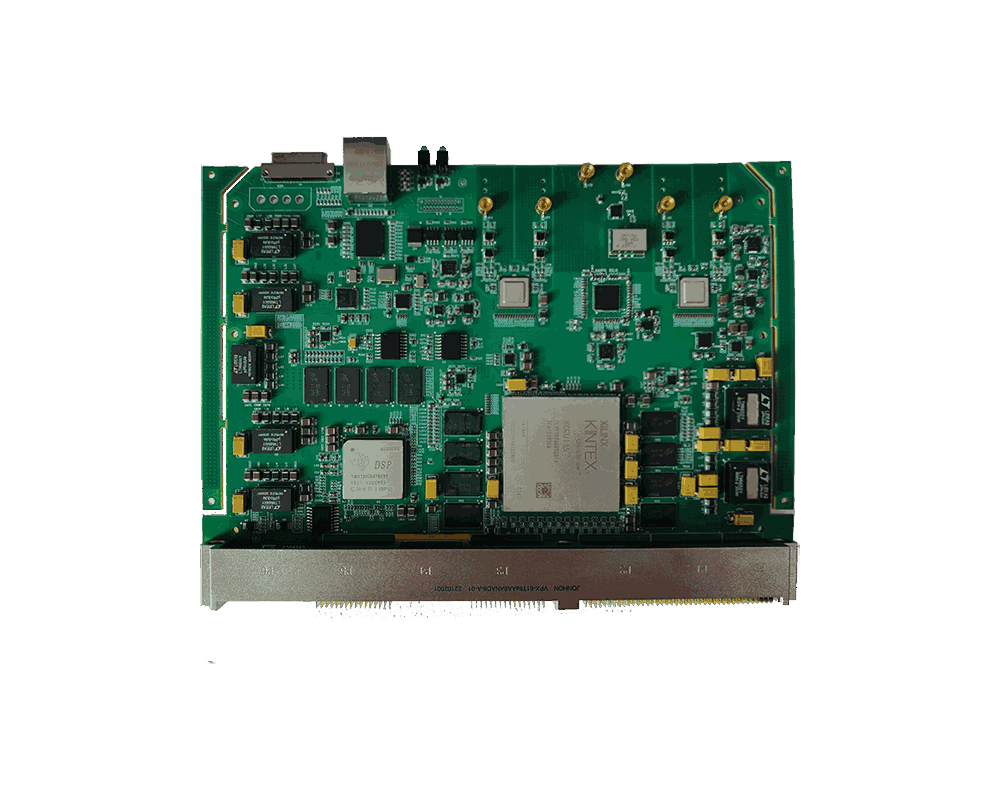

本项目主要开发一款基于XilinxML605以及FMC扩展ADC采集板架构的ADC芯片测试平台,任务包括逻辑开发以及相关软件开发。

逻辑部分包括以下部分:

1.基于XILINXML605开发板。

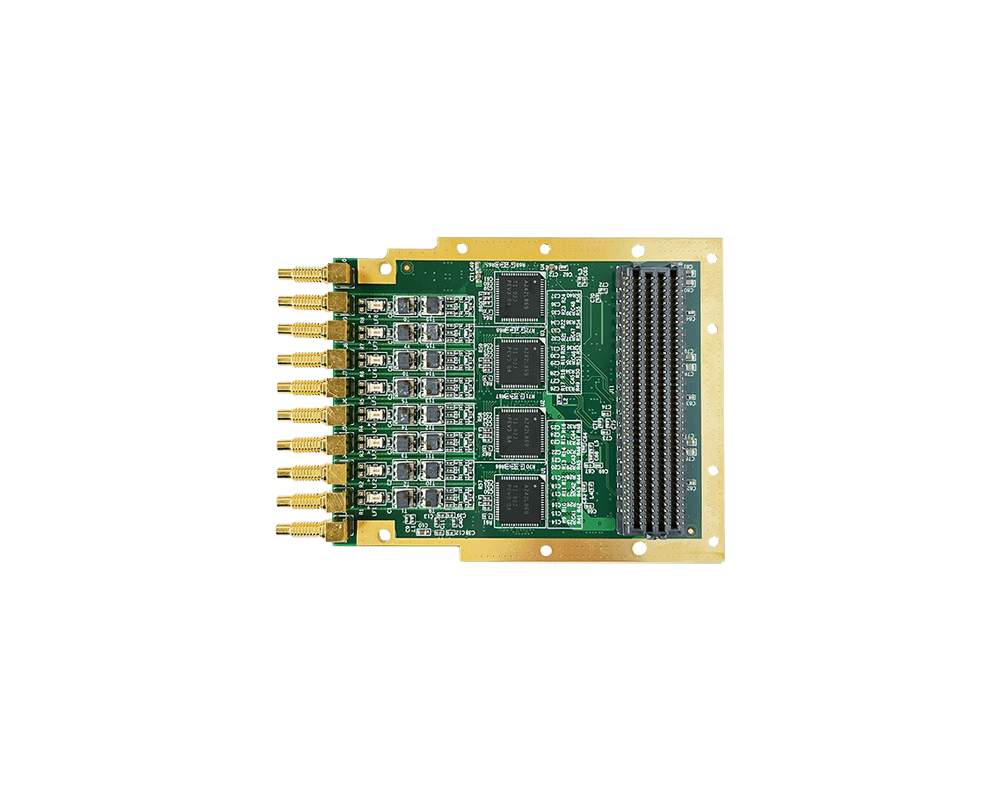

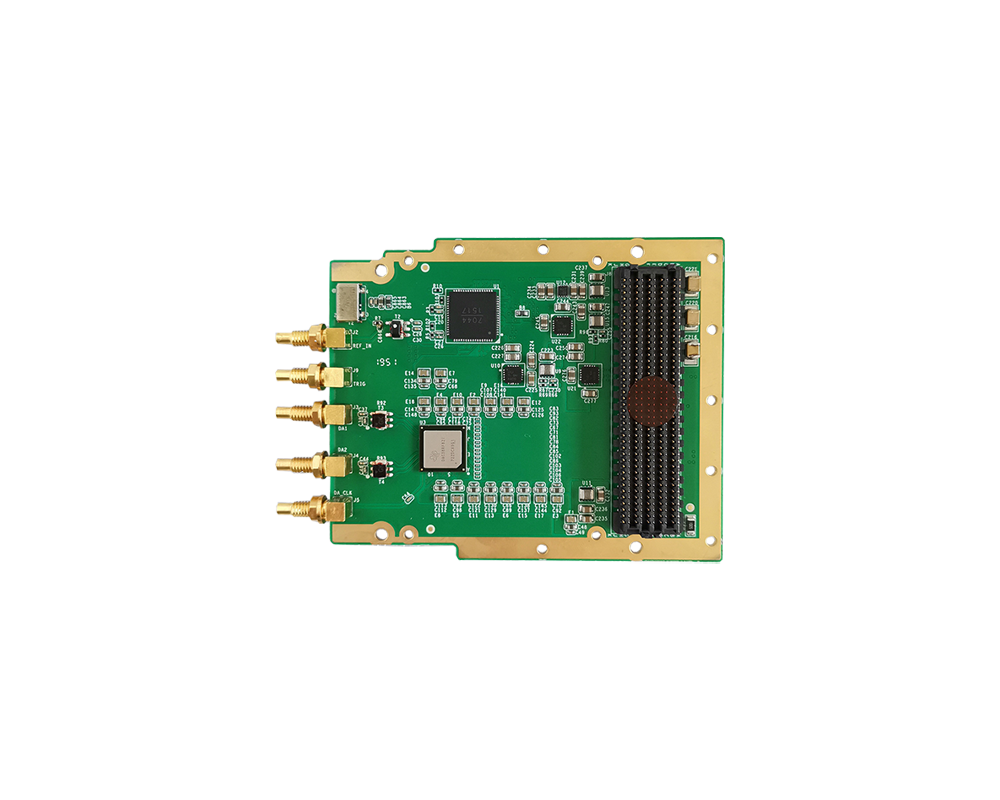

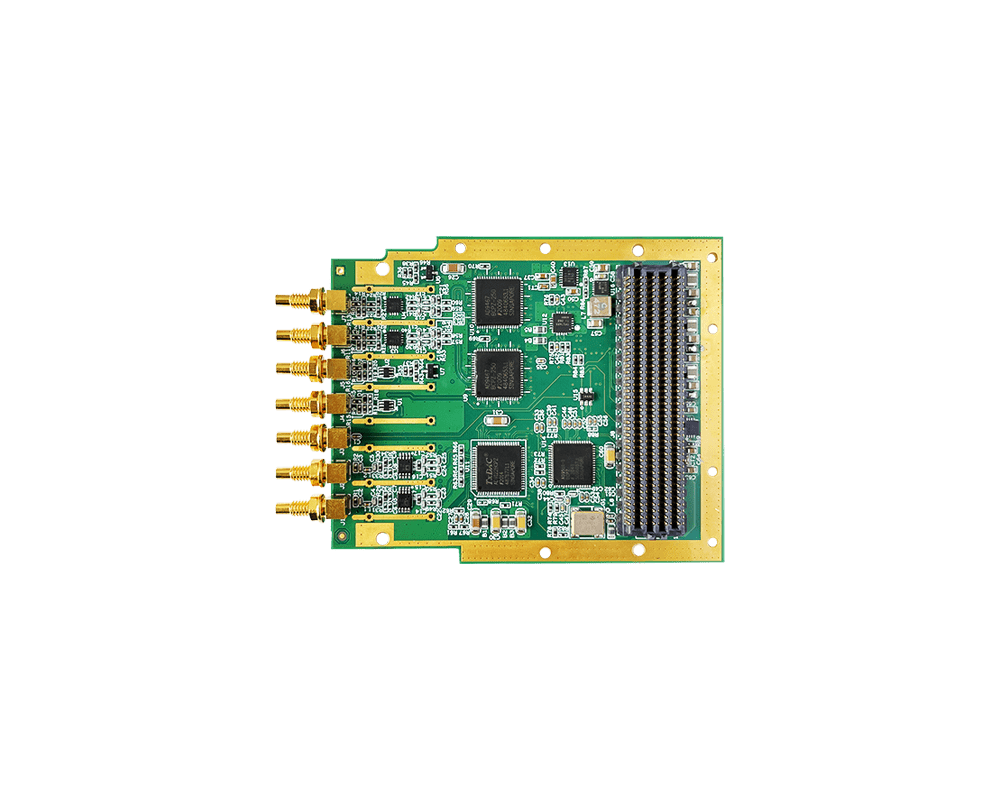

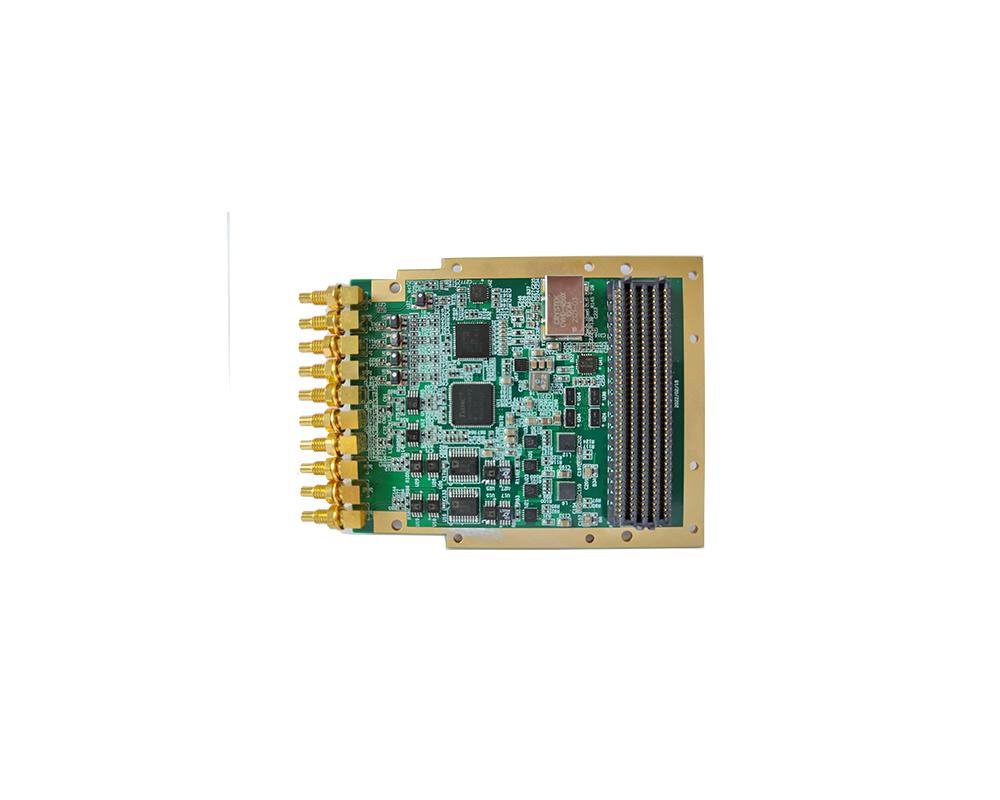

2.支持扩展FMC子板,支持16bit250Msps以及14bit400MspsADC输入。

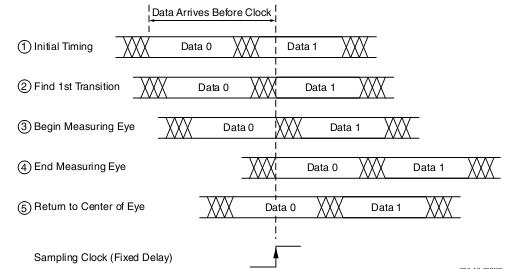

3.ADC输入接口支持数据/时钟相位动态自适应调整。

4.支持64位宽DDR3控制器,数据率为DDR31066MHz-1000MHz。

5.支持PCIE1.0x8,支持PCIeDMA操作,PCIex8模式下,DMA传输速率为1000MB/s左右。

6.数据传输模式支持数据长度模式可以配置。

7.通过SPI配置周边器件,支持8位、16位、24位及32位协议,支持上沿和下沿选择。

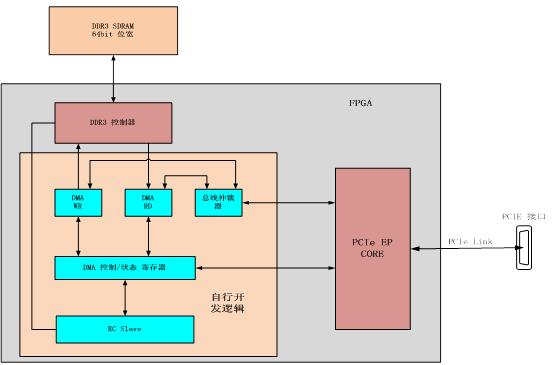

二、逻辑系统框图

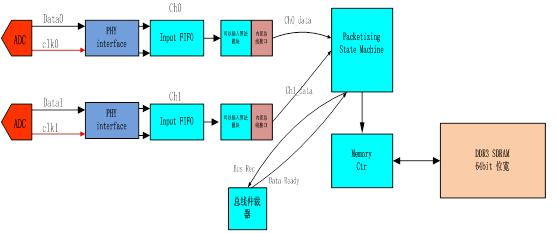

三、关于模拟前端接口逻辑:

模拟前端接口同外部模拟端口连接,接口模块分为phy和控制逻辑部分:

ADC接口随路时钟支持动态相位调整,系统初始化或温度变化时,会采用自适应的方法动态调整随路时钟和ADC数据的相位关系,保证数据采集的正确性。结构如下:

ADC通道分别设置每个通道工作或不工作,状态可读:通道当前激活状态以及ADC数据是否溢出。

128位宽数据输出下每个采样点10-16位宽格式

l单通道数据格式:

A0A1A2A3A4A5A6A7

A8A9A10A11A12A13A14A15

........

四、关于DDR3SDRAM

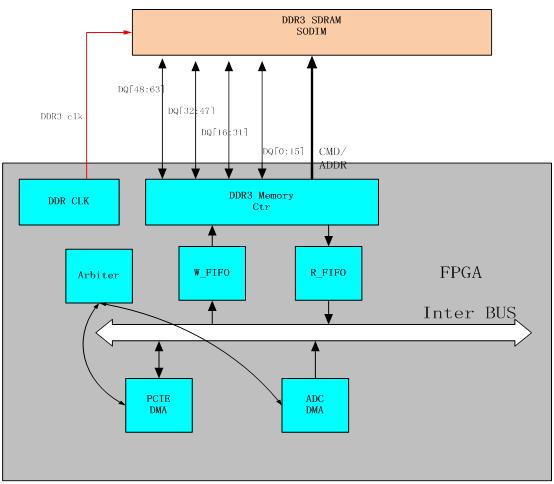

MemoryController核心模块采用MIG。模块对接TXFIFO和RXFIFO,采用多通道形式,通过内部高速总线互联,总线具有仲裁功能;支持ADC通道和PCIEDMA通道同时申请读写DDR3存储设备。

其组成形式如下图所示:

五、关于采集模式:

采集模式支持标准工作模式:

标准工作模式设置:

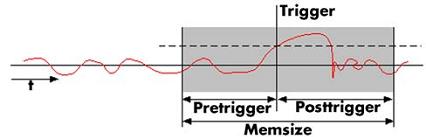

设置单次采集长度Mem-size;

设置触发Post-trigger点数;

Pre-trigger=mem-size-Post-trigger

采集过程如下所示:

六、关于触发模式

软件触发:

通过PC及控制软件产生触发信号。

七、外部控制接口

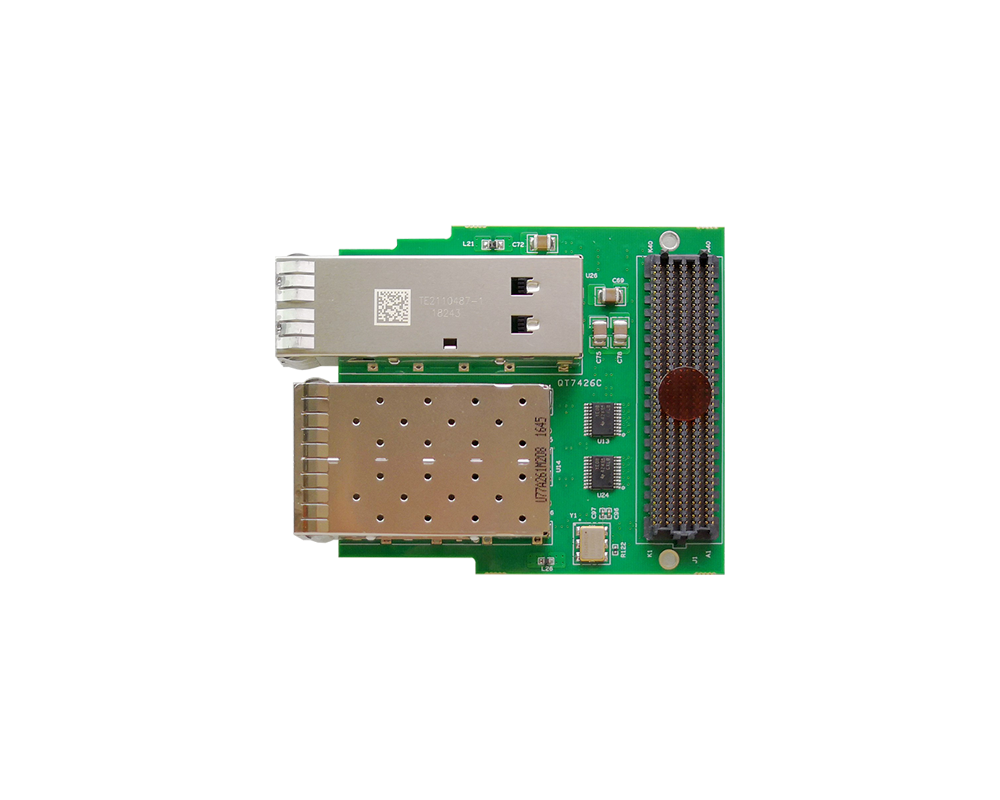

外部控制接口/通信接口主要包括以下部分:

1.SPIMaster

2.GPIO/DIO

八、PCIE总线部分

PCIE控制器主要分为两部分:

1.PCIEendpoint,采用XilinxFPGA中的硬核完成。

2.PCIEDMA部分,需要开发,完成符合项目需求的DMA控制器逻辑单元。

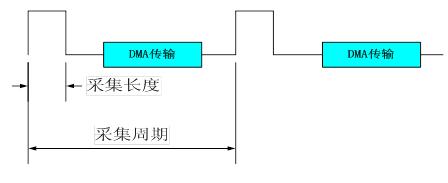

为了扩展需要PCIE模块支持1x、4x和8x传输,PCIE模块结构如下图:

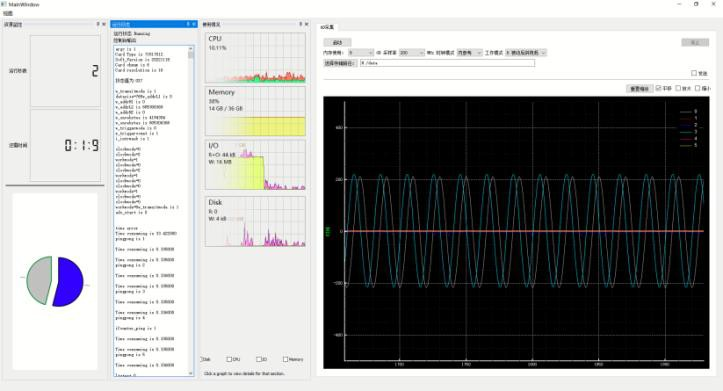

九、关于系统软件

同逻辑配套的系统软件功能如下:

1.支持Windows32bit/Windows64bit的设备驱动。

2.支持LabView。

3.提供CommonLibrary支持基本操作。

4.提供TextbasedAppication例程,支持VisualC++。

整体结构如下:

2.驱动程序函数定义:

lhOpen()openHWdevice

lhClosecloseopeneddevice

lSetParam_i32setsoftwareregister(32bit)

lSetParam_i64setsoftwareregister(64bit)

lGetParam_i32getsoftwareregister(32bit)

lGetParam_i64getsoftwareregister(64bit)

lDefTransferdefineabufferforafollowingdatatransfer

lGetErrorInfothefunctionreturnscompleteerror

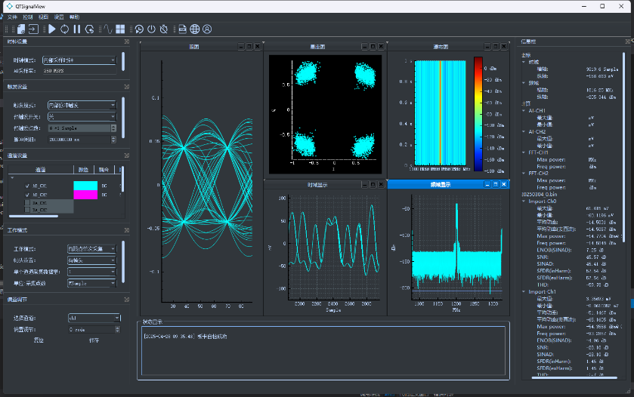

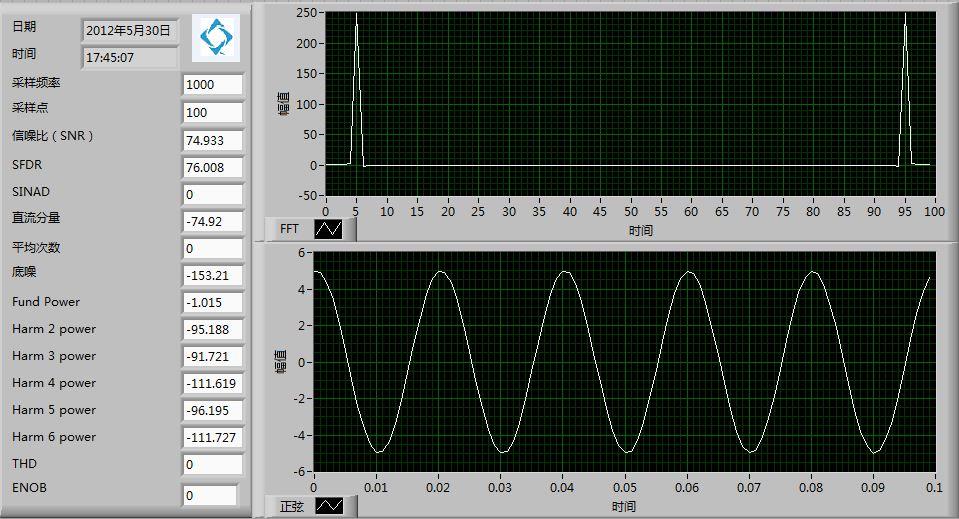

十、ADC性能测试:

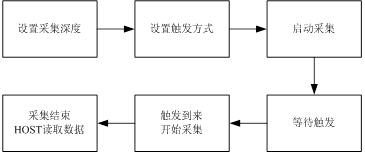

采集控制设置:

l采集长度

l采样率

l开始/停止

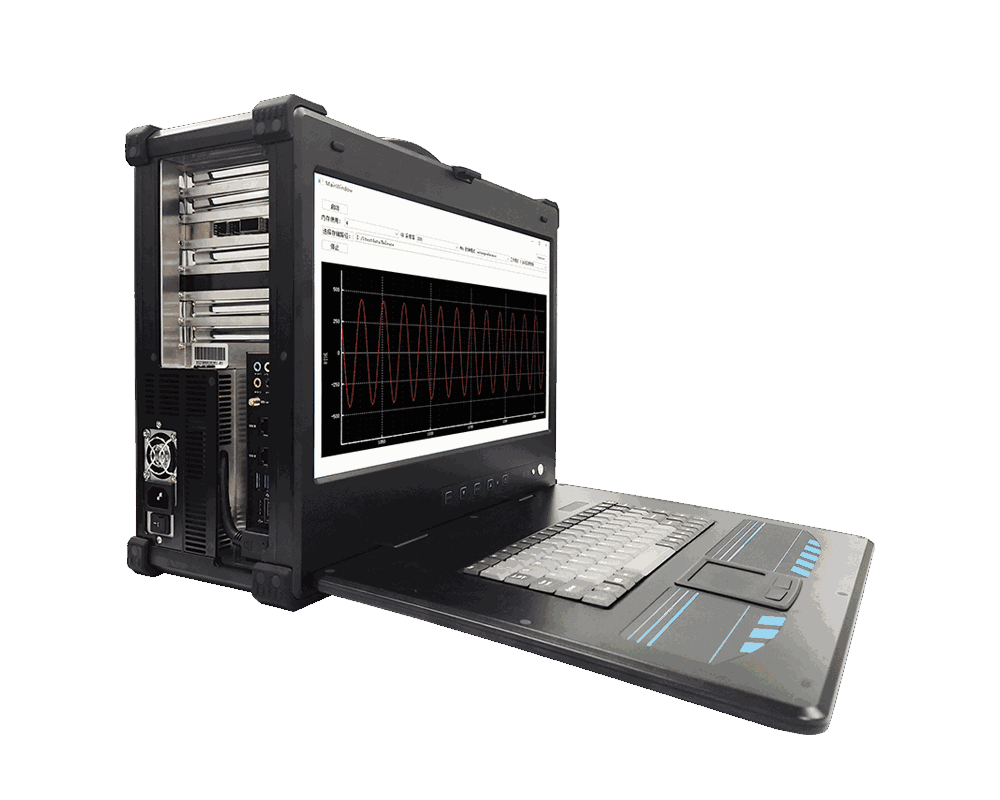

ADC动态指标测试如下图:

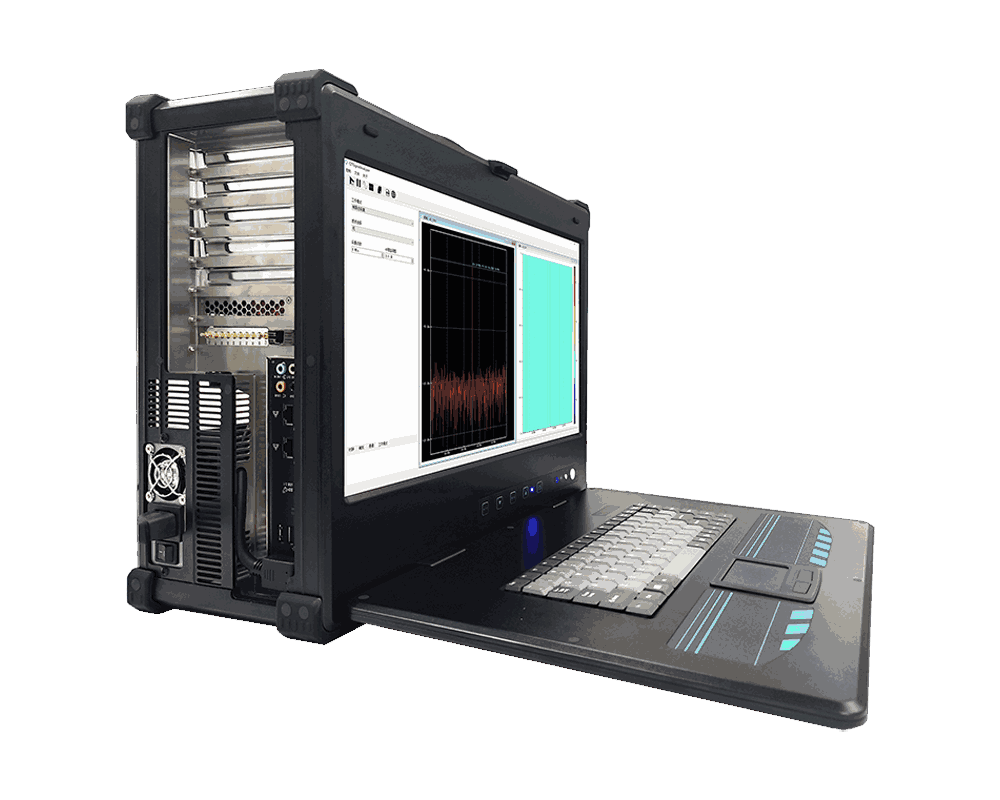

ADC静态指标测试如下图: