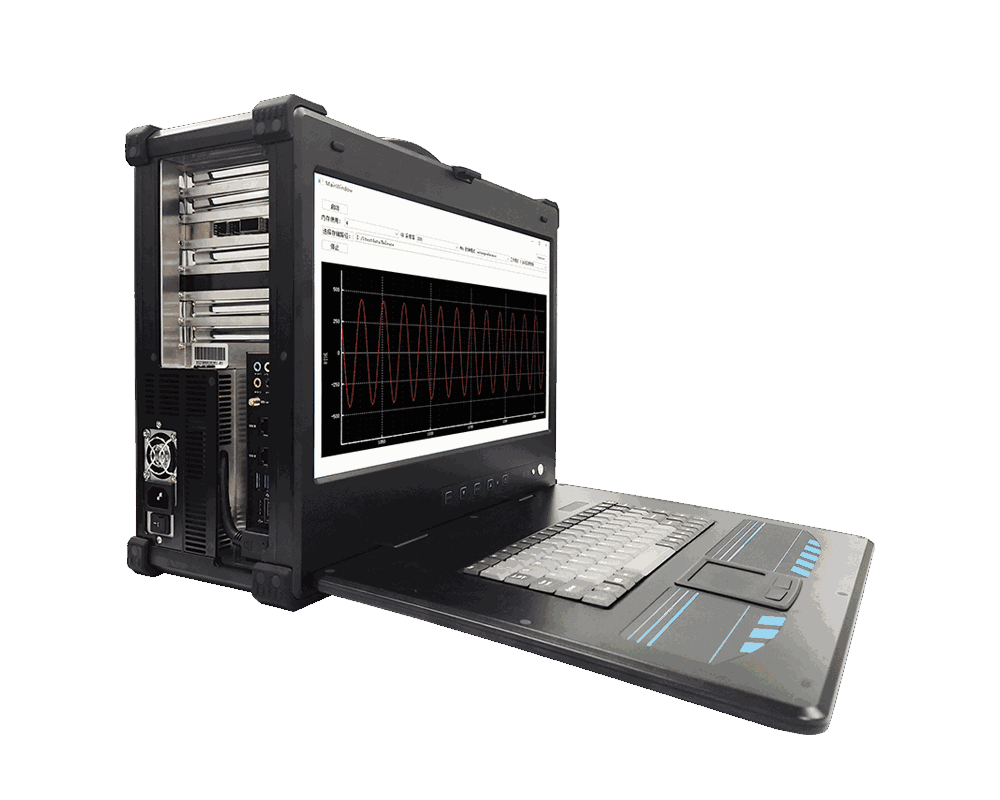

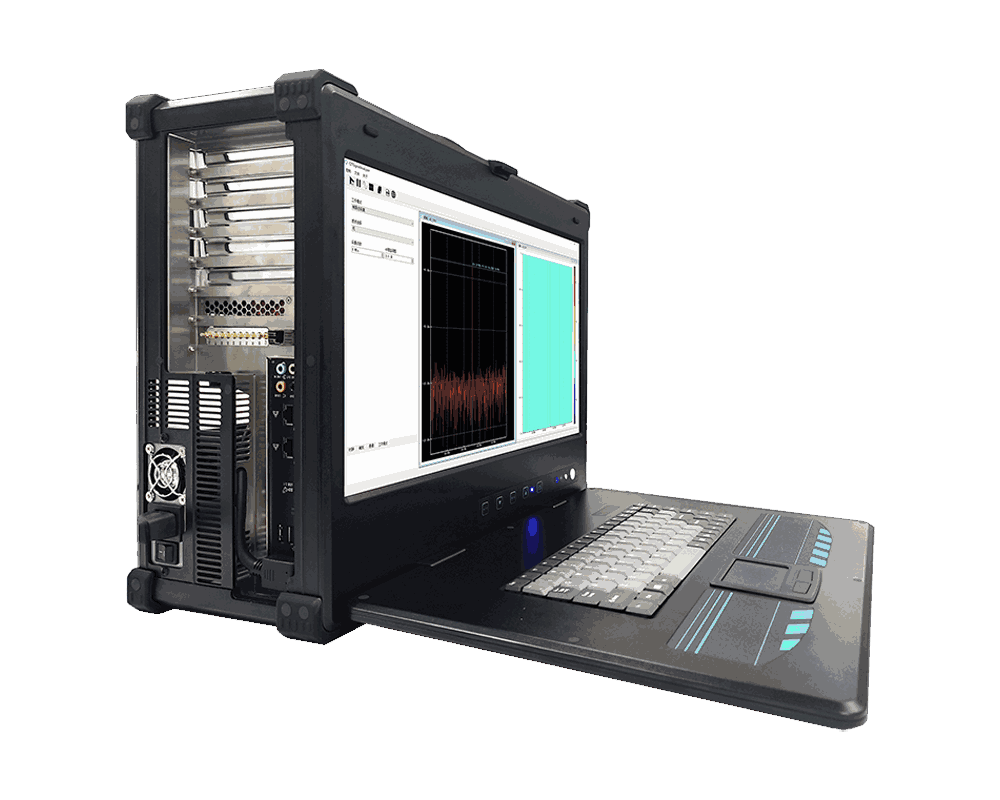

超带宽MIMO通信测试系统

超带宽MIMO通信测试系统

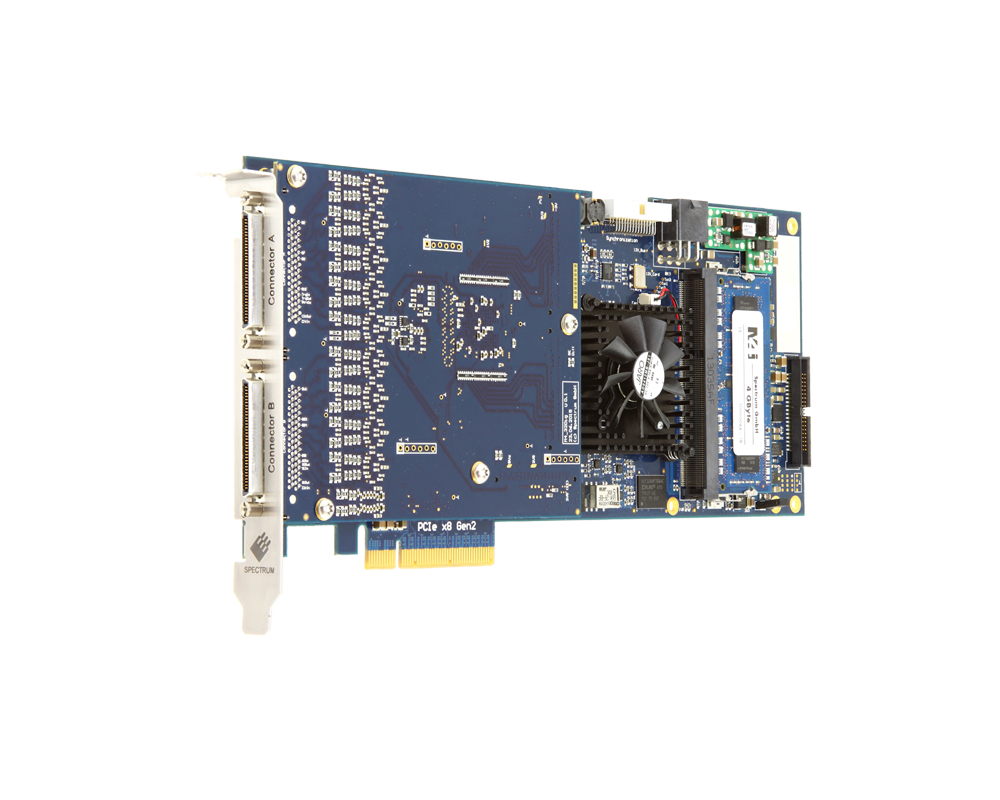

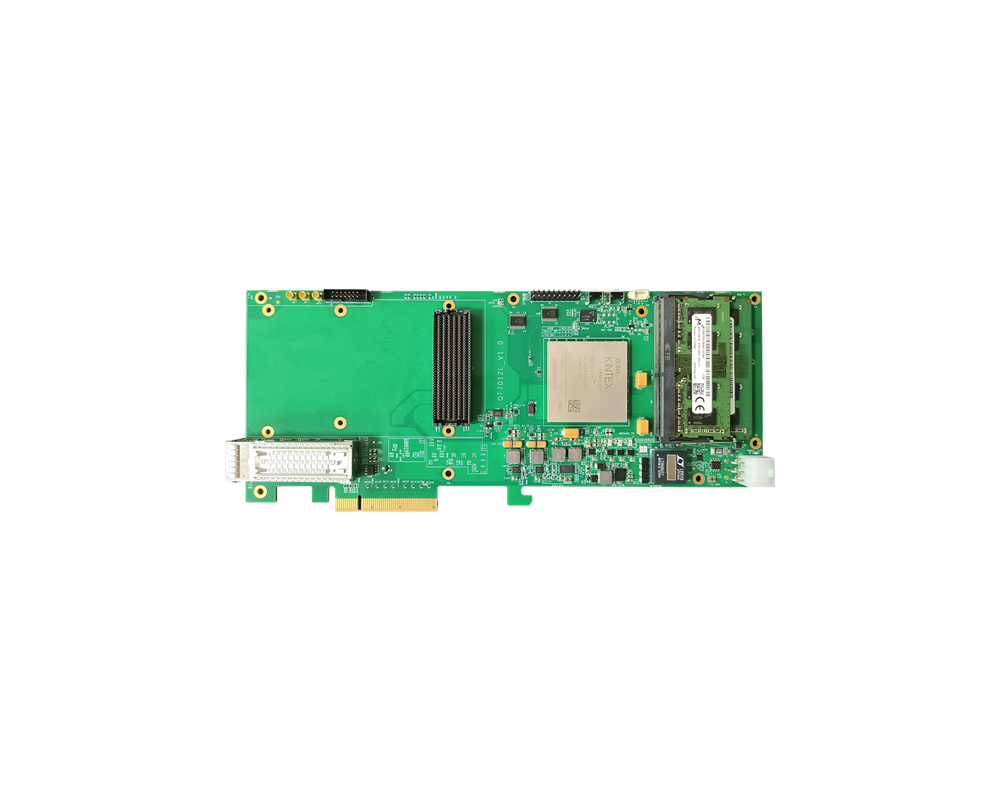

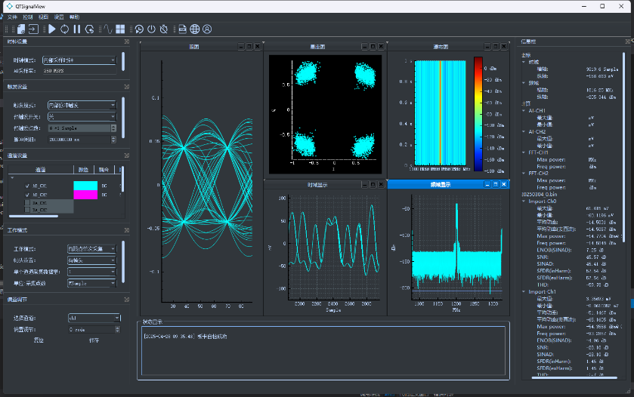

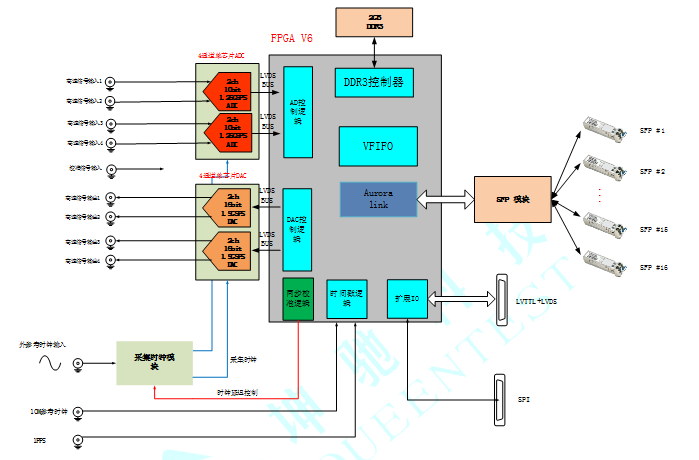

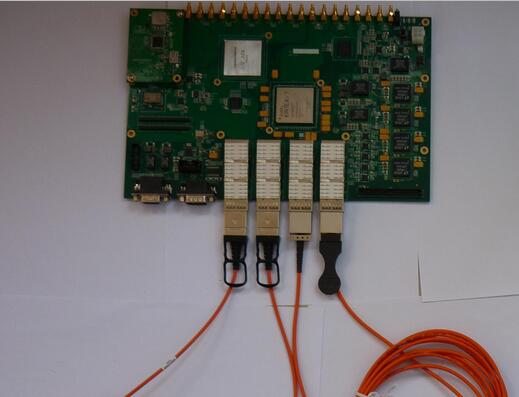

基于光纤接口的超带宽MIMO通信测试系统可以完成4路宽带信号收发(两对IQ信号)测试,并进行基于FPGA的实时数据处理的目的。其中AD通道采样率为10bit,1.25GS/s, DA通道为14bit, 1.5GS/s。

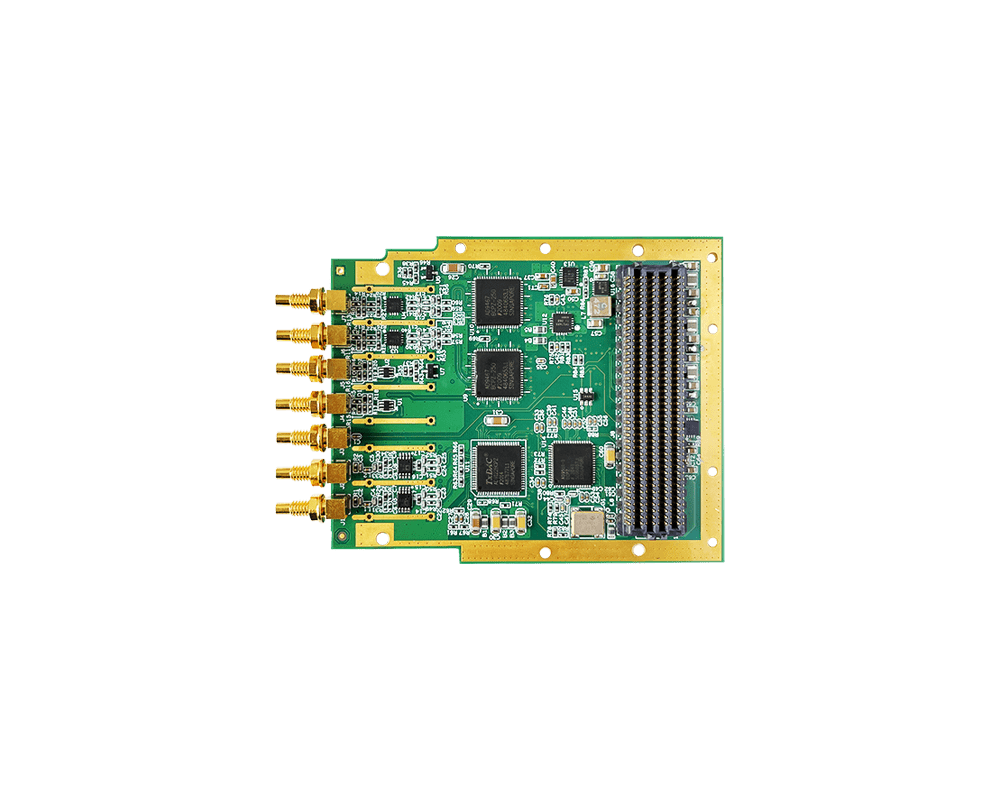

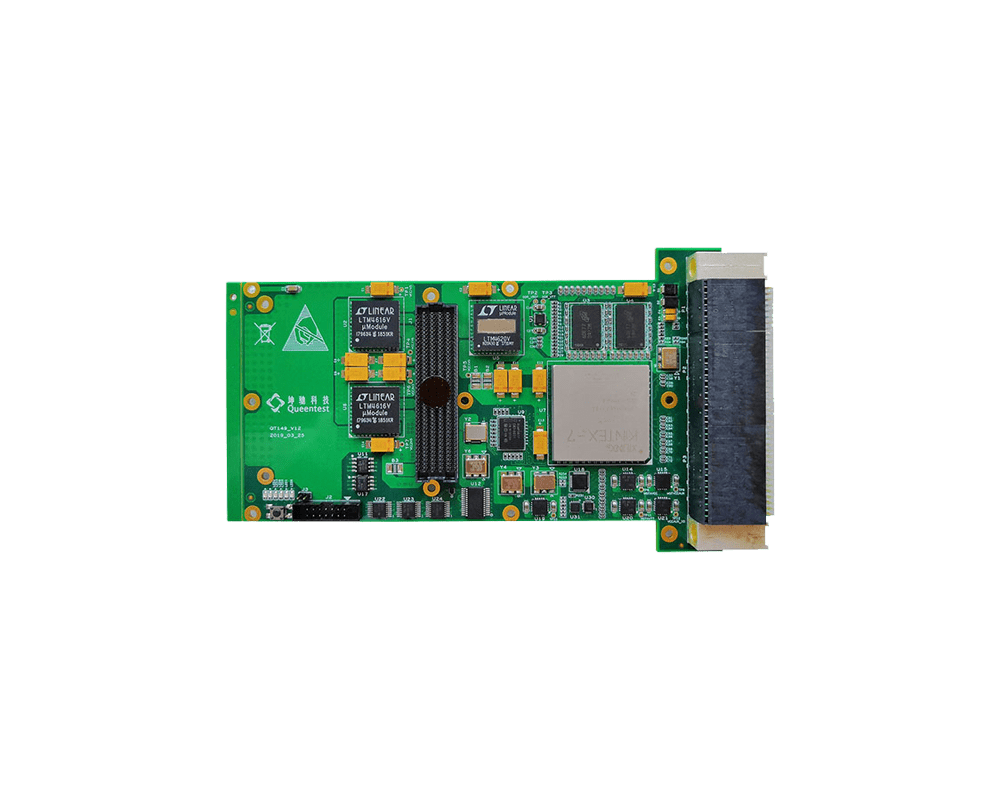

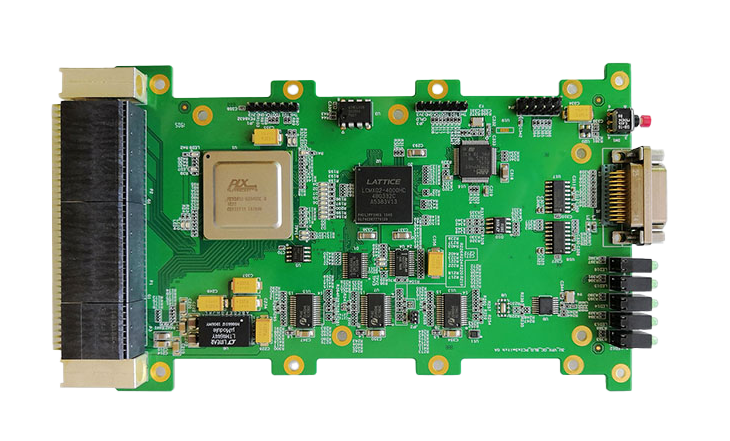

采集模板规格:

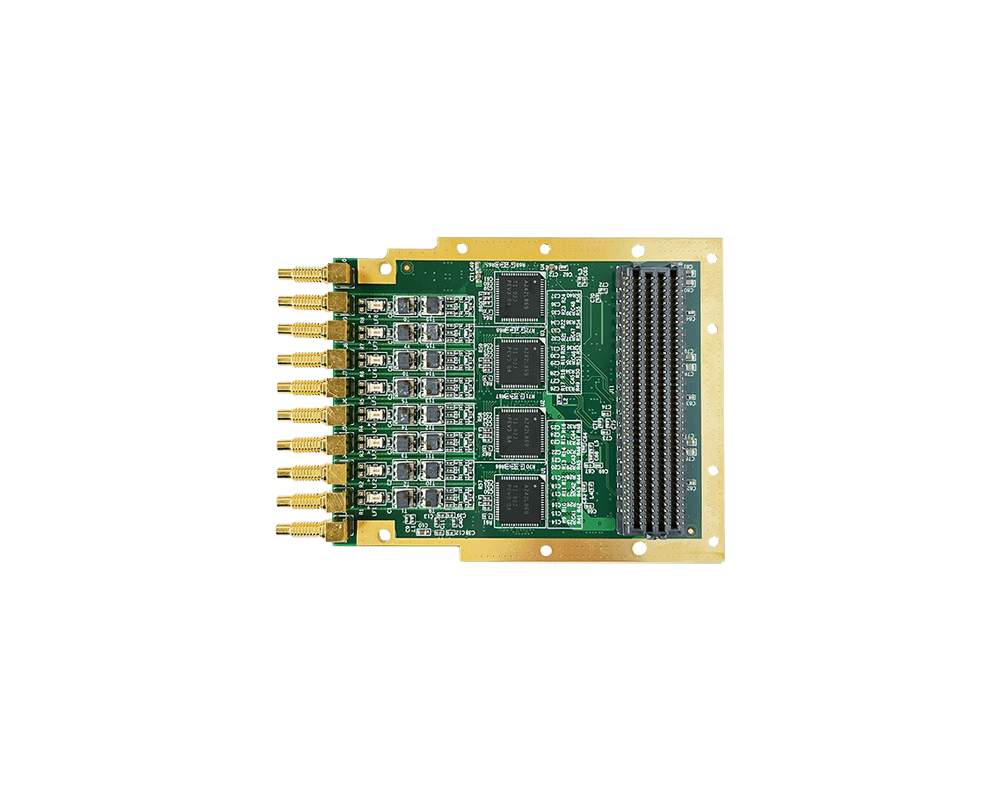

每个模块集成4通道10bit 1.25GSPS ADC采集。

同时支持两对IQ信号输入,采用交流差分藕合输入方式。

同步模板规格:

同步采集校准系统。

统一的基准时钟和触发信号分发。

采集模板实现框图如下:

ADC规格如下:

ADC型号:EV10AQ190A

ADC输出位数:10bit,4通道采样率1.25GSPS

模拟带宽:LF~2GHz

输入阻抗:100欧(差分),AC藕合

输入形式:SMA,差分输入

满量程输入幅度:500mVpp

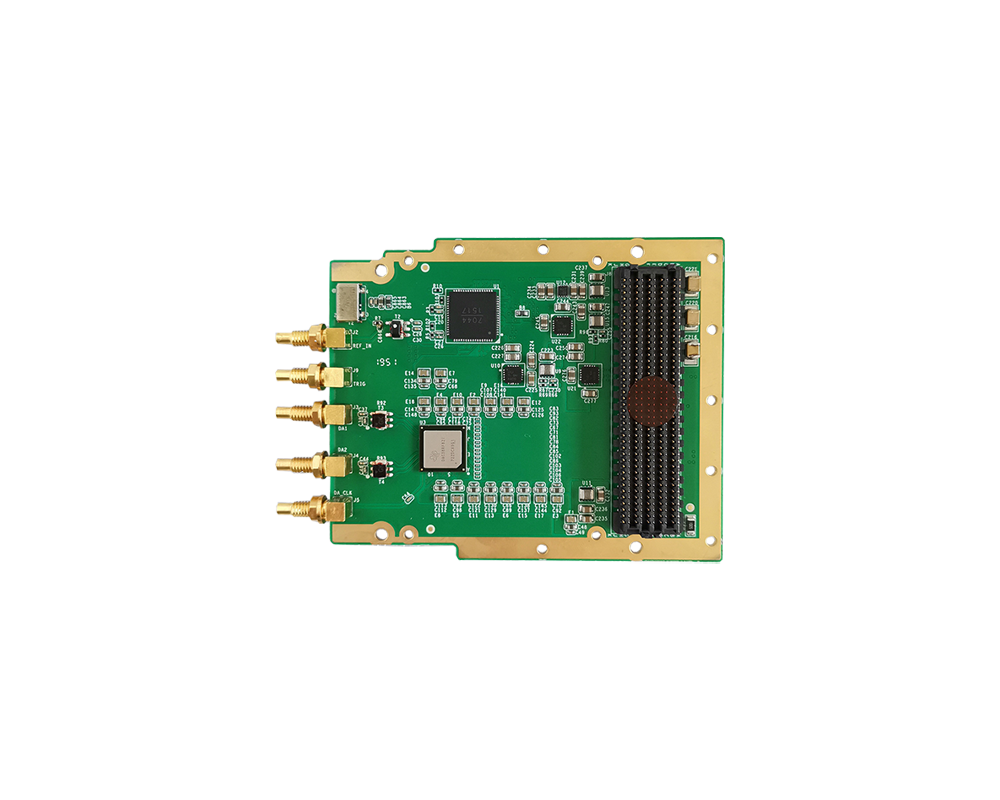

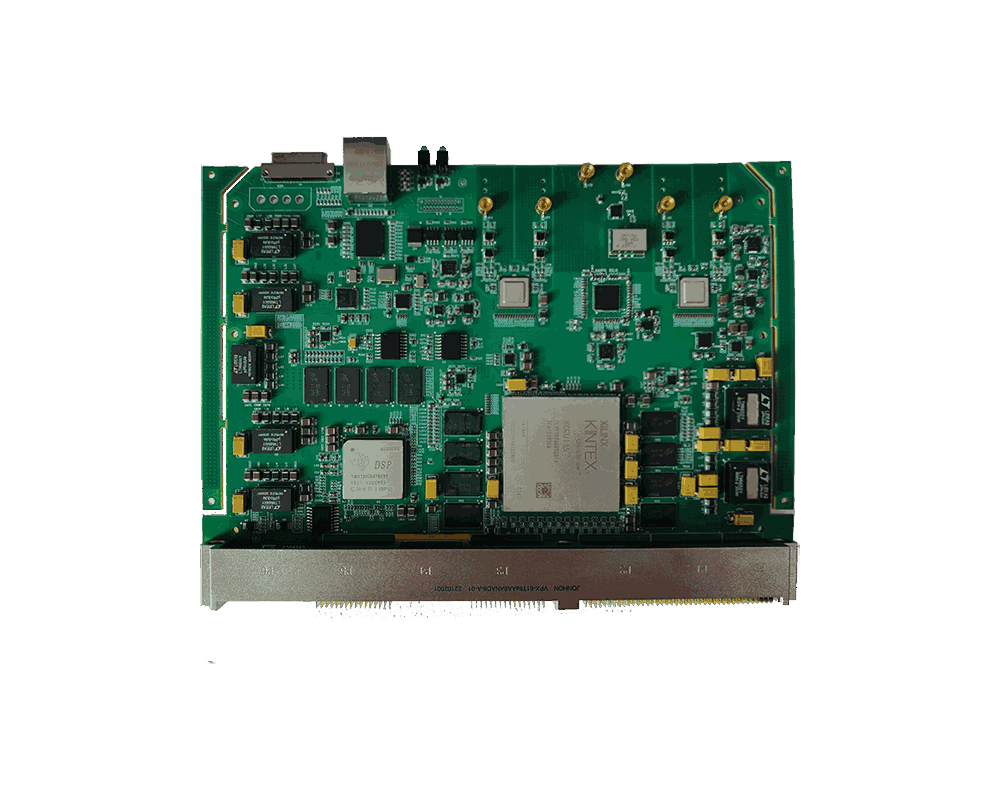

DAC规格如下:

DAC型号:DAC34SH84

DAC输出位数:16bit,4通道采样率1.5GSPS

输出阻抗:100欧(差分端),AC藕合

输入形式:SMA,差分输出

满量程输出幅度:500mVpp(单端),1Vpp(差分)

具有同步触发和外参考时钟输入的采集时钟模块:

该模块为单独一个PCB子板,可以方便更换。当更换为不同VCO型号时,可以支持灵活的输出采样时钟,覆盖2.5GHz~到1080MHz(时钟时采样率的2倍)。

扩展IO:

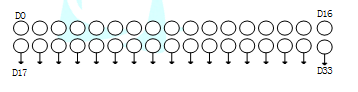

1.DIO

17个

兼容2.5V LVTTL和LVCMOS

连接器:单排2.54mm通用连接器。

排列如下:

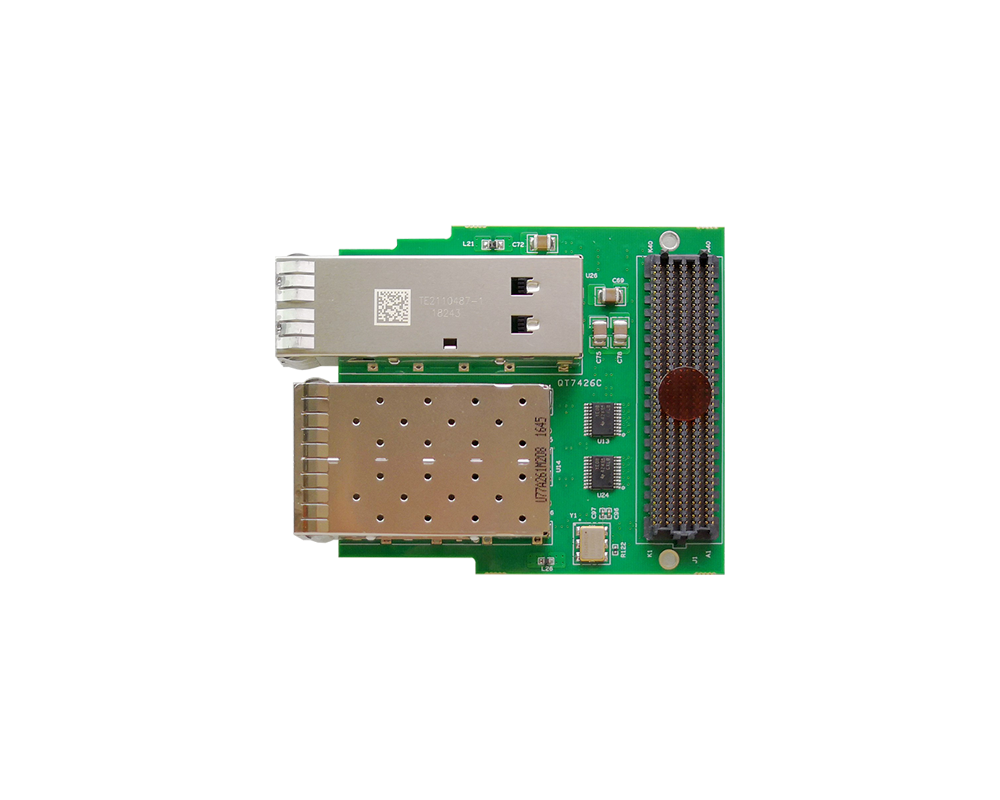

2.高速LVDS输入输出

数量25对

LVDS速度1.25Gbps

连接器:高密度连接器带连接电缆

3.SPI接口

定义为4线SPI,S_CLK、S_DIN、S_DOUT、S_EN。

3.3V TTL电平。

连接器:8pin 2.54mm连接器。

4.状态LED

4个LED直接连接到FPGA上用于显示。

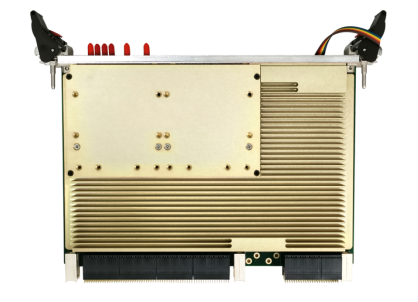

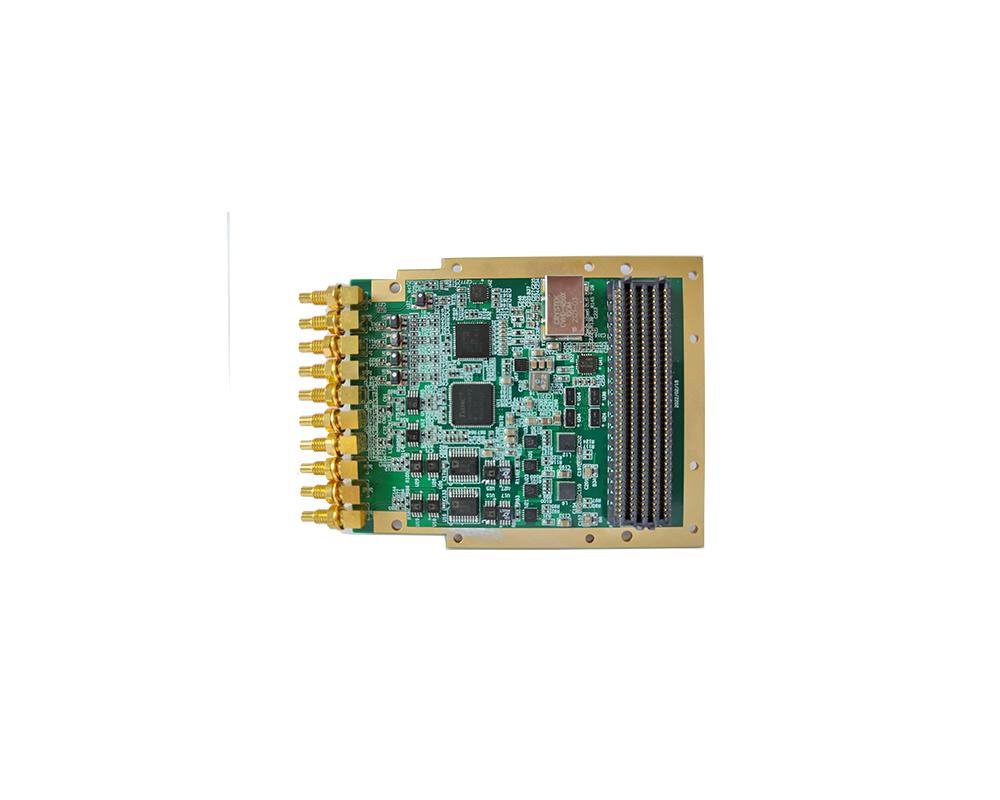

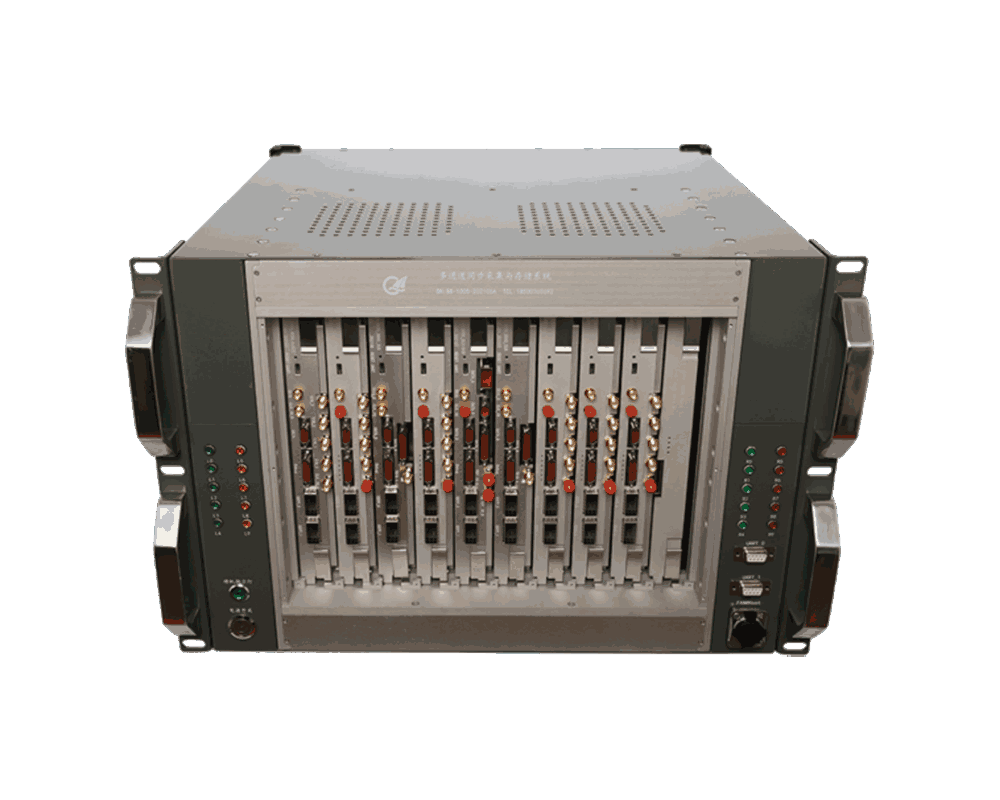

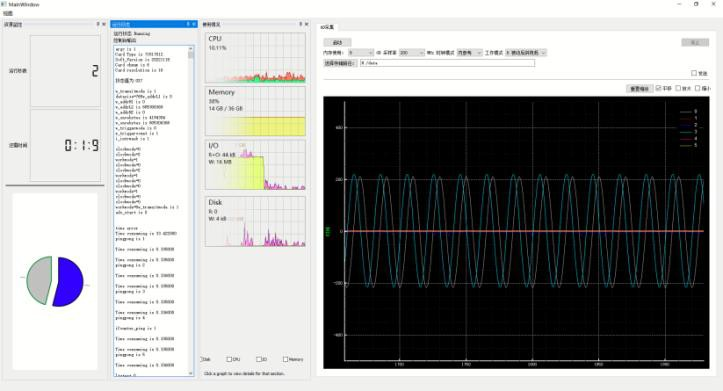

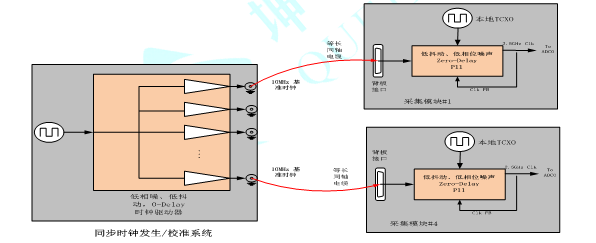

同步模块:

产生同步四个采集模块的基准时钟和同步信号

同步校准信号发生

通过自动调节芯片内部的延迟来达到输出时钟和参考时钟的相位一致性。

没有进行zero delay补偿的时钟输入/输出相位误差约为664ps,这个误差是一个范围,可能在0-644ps中随机出现!经过zero delay补偿的相位误差如下图:

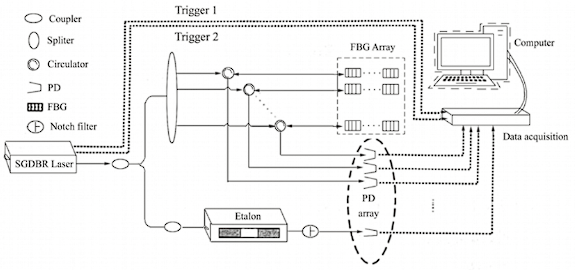

关于秒脉冲同步控制:

GPS同步模块由以下部分组成:

GPS接收模块:输出1pps秒脉冲

本机恒温晶体:输出10MHz

时钟驯服模块:根据GPS输出的1pps信号,同步每个采集模块的本地恒温晶体;同时产生1s频率的

同步时钟信号。

保障在GPS卫星短时间失锁情况下仍然能维持同步稳定

采集间模块同步机制:

同步原理如下图所示:

同步机制在采集模块FPGA内实现,采用两种方式实现同步:

时间戳模式:驱动时钟为采集时钟,频率1.25GHz,FPGA2/4分频处理,当有触发事件时,锁存时间戳计数器,将该计数器值同ADC数据值上传服务器。GPS同步模块输出的同步脉冲负责每秒为计数器清除一次,保证各个采集模块的计数器同步。如果各个采集模块是同时满足触发条件的,此时各个通道的计数器值应该相等。

绝对时间记录模式:触发脉冲输出到GPS绝对时间计数器中;当绝对时间计数器检测到上升沿,锁定绝对时间计数器,然后通过总线形式读取当前时间,同ADC采集数据上传主机。