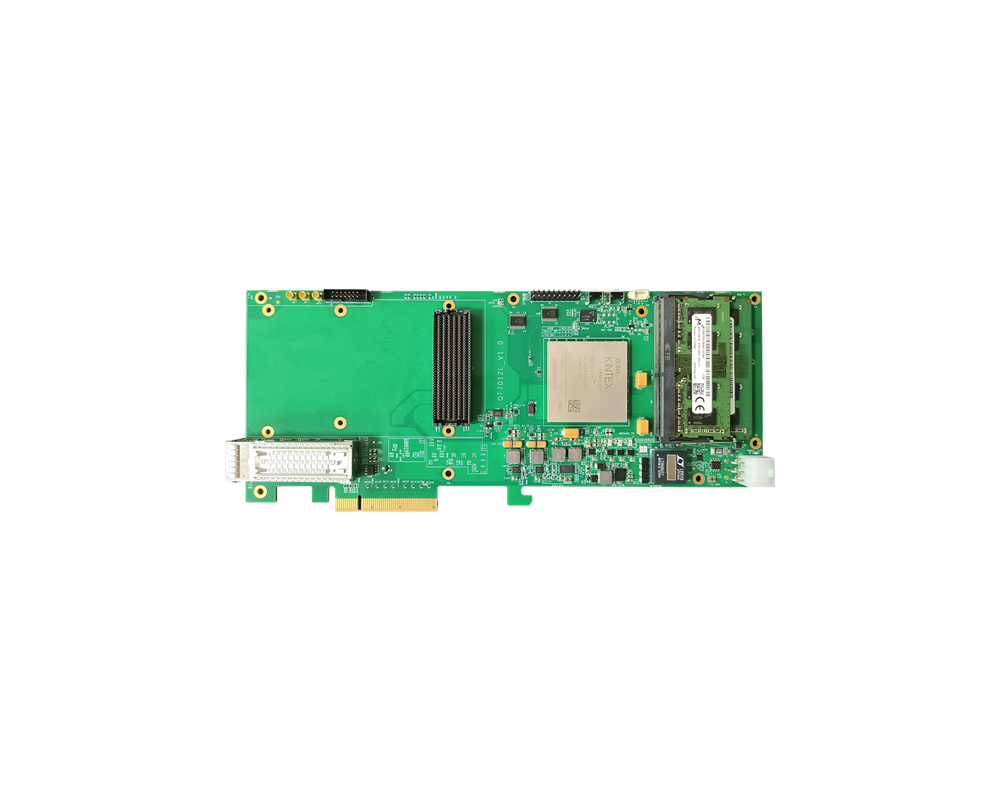

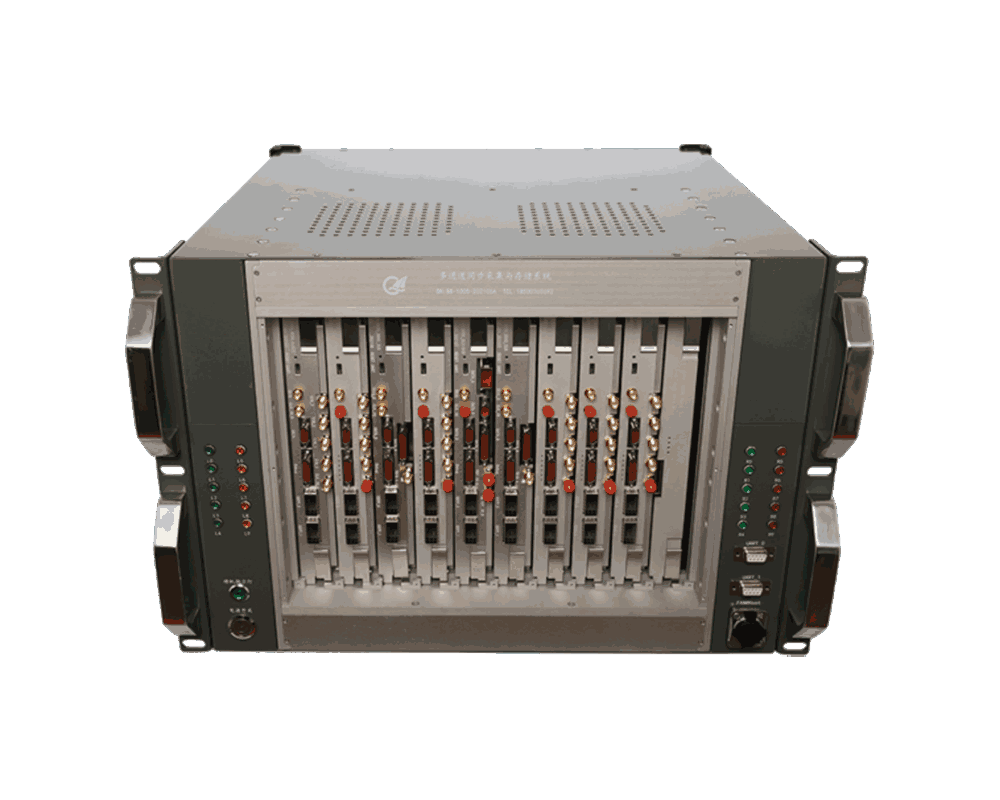

基于PCI Express的高速采集测试系统

采集系统规格:

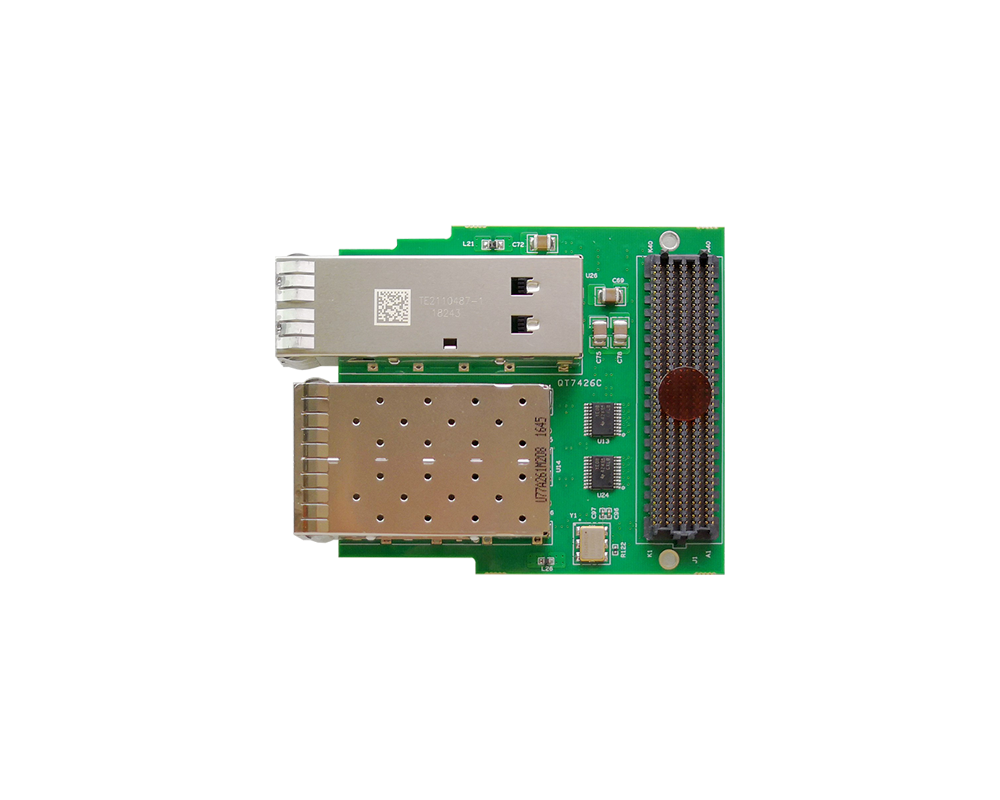

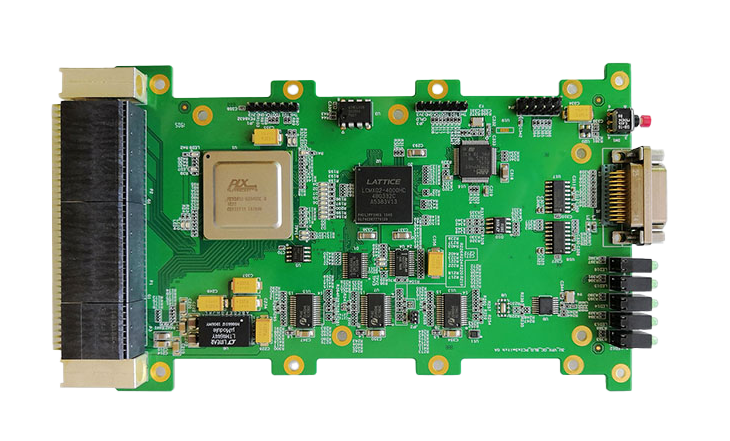

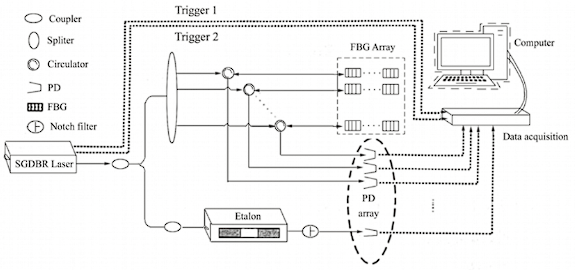

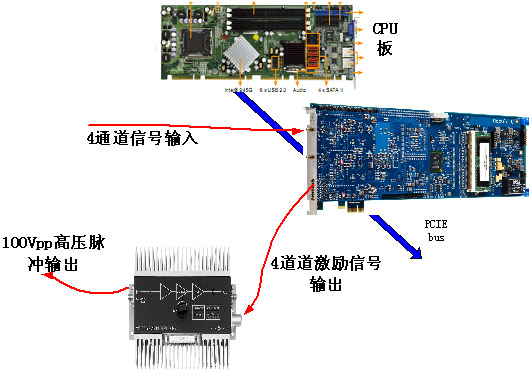

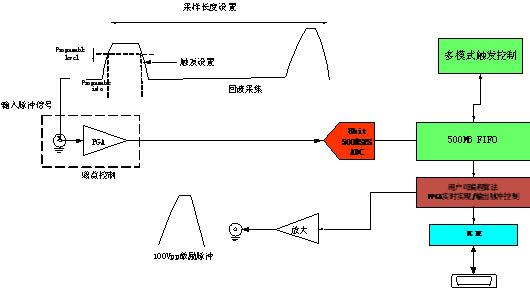

系统基于PCIExpress总线结构,包括如下几个部分:

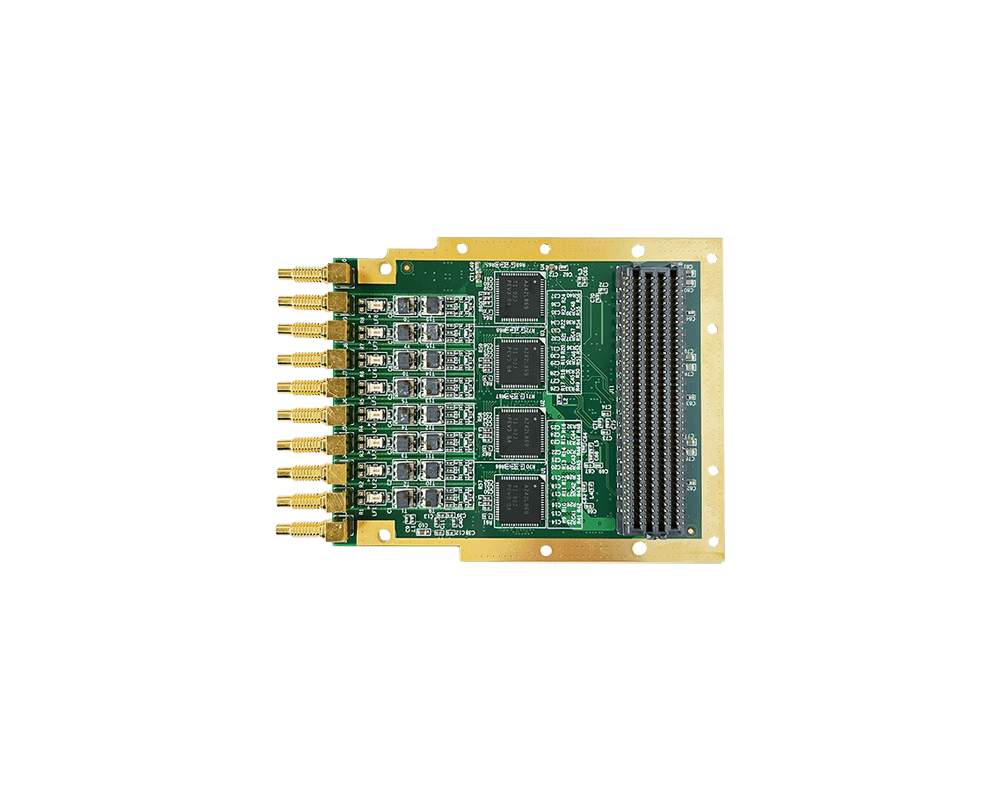

1.4通道8bit500Msps同步采集,标准PCIe全长卡尺寸;

2.4个高速IO,产生激励脉冲输出。

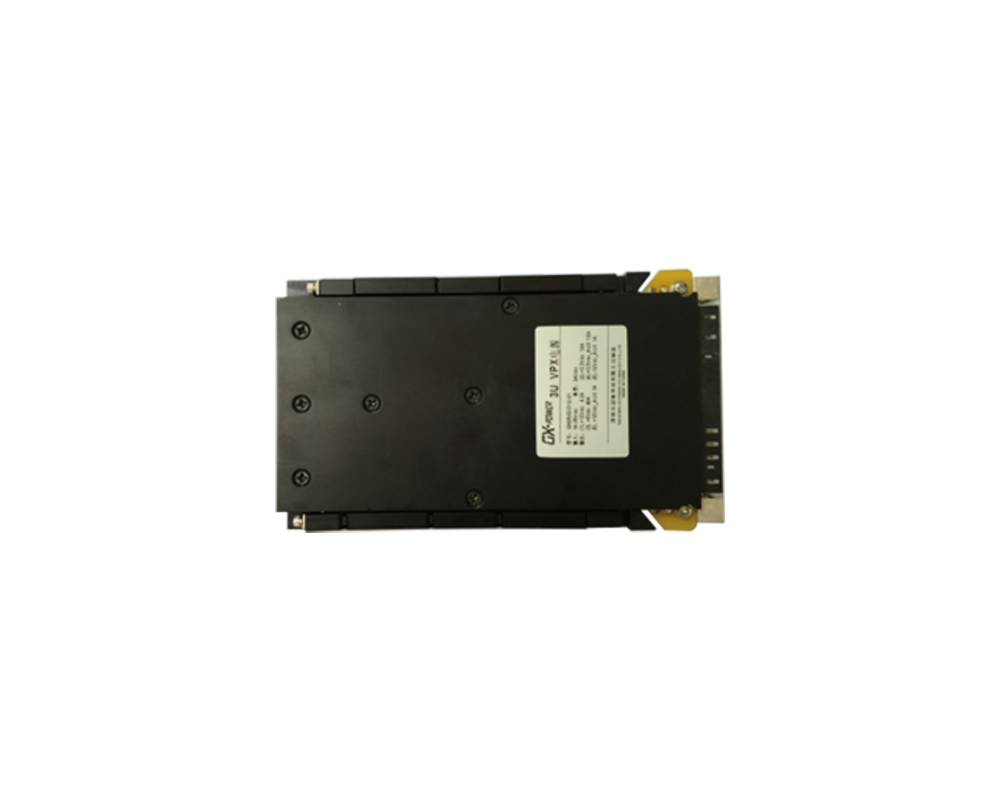

3.外置脉冲放大器,输出100Vpp的激励短脉冲。

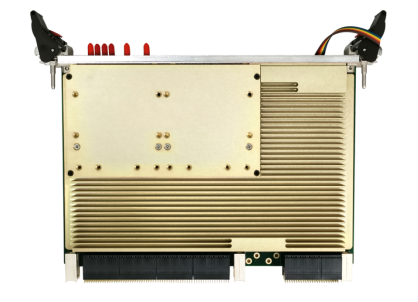

4.基于PCIExpressx8总线的工控机。

系统实现框图如下:

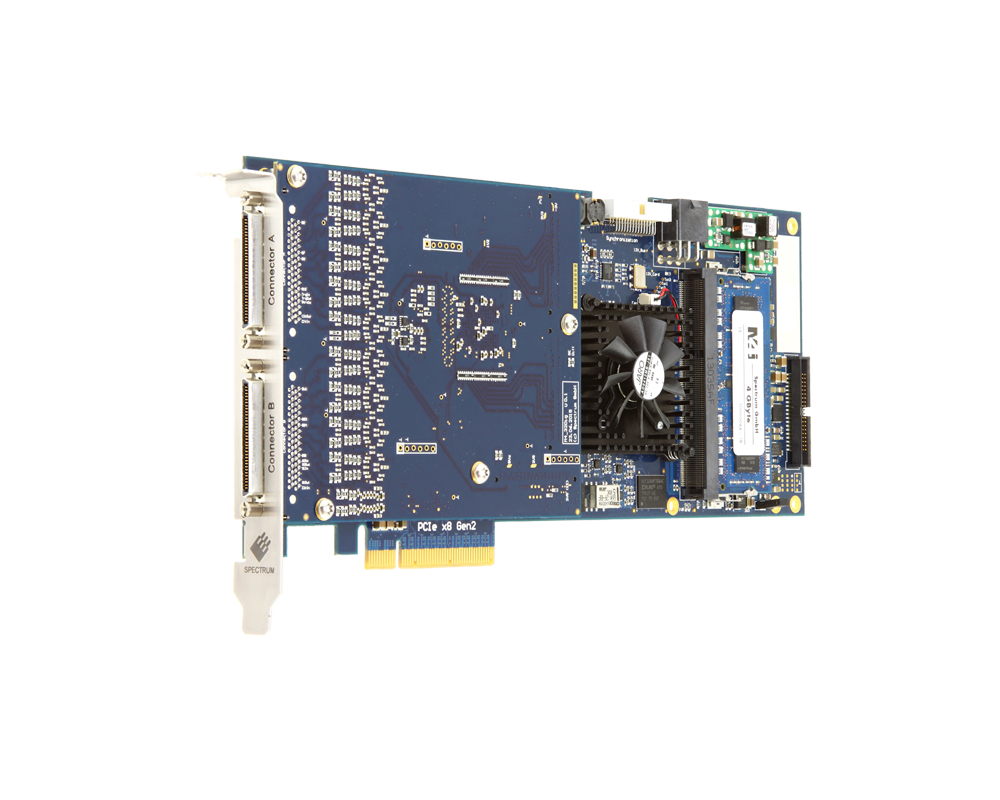

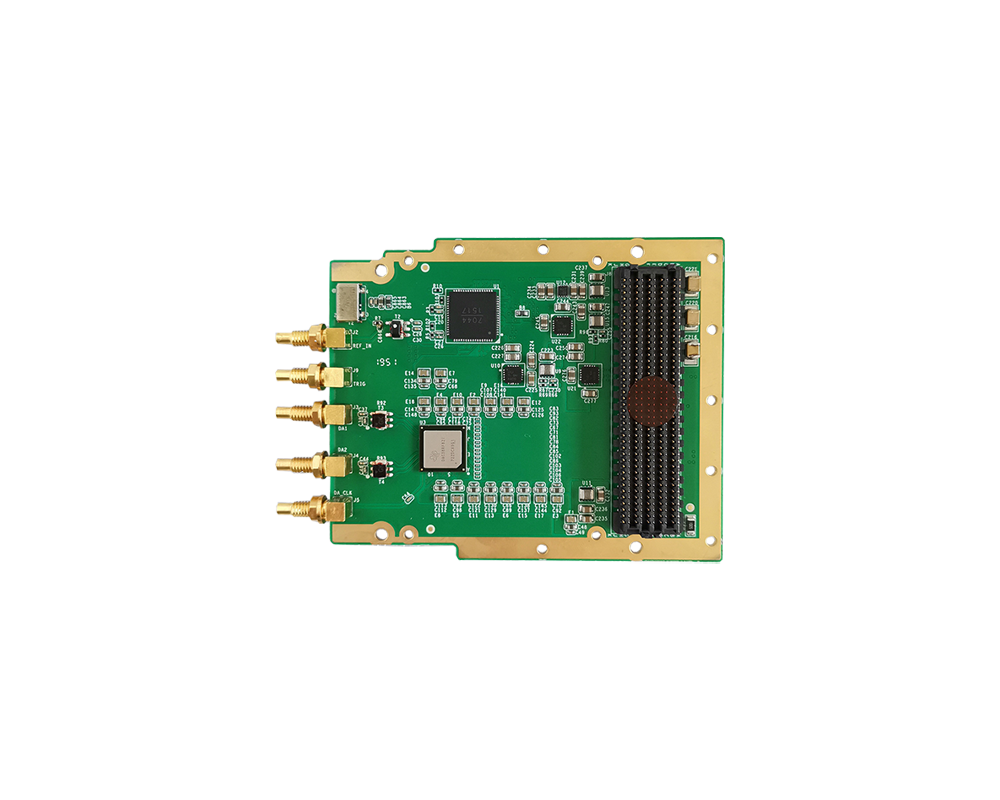

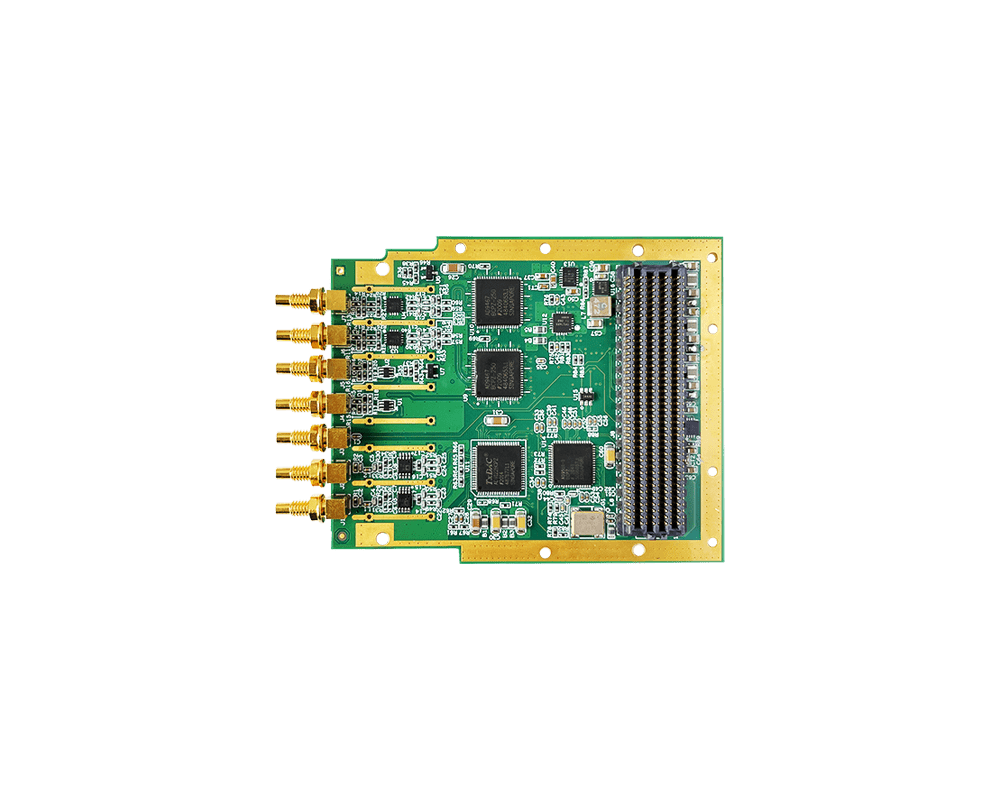

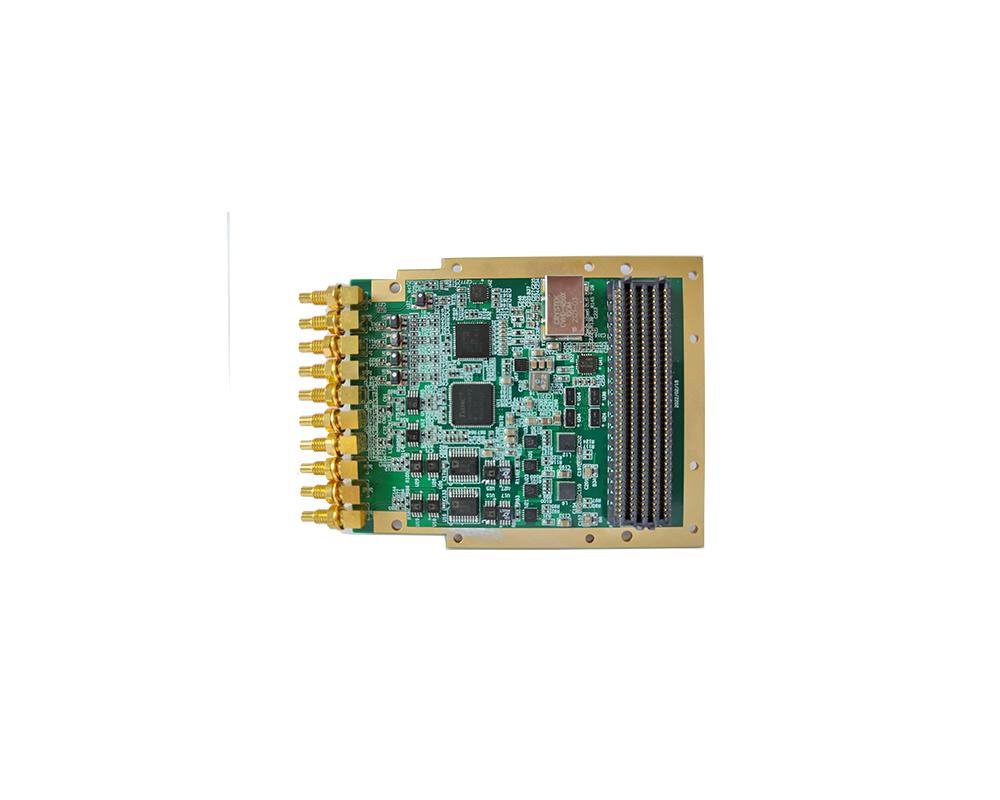

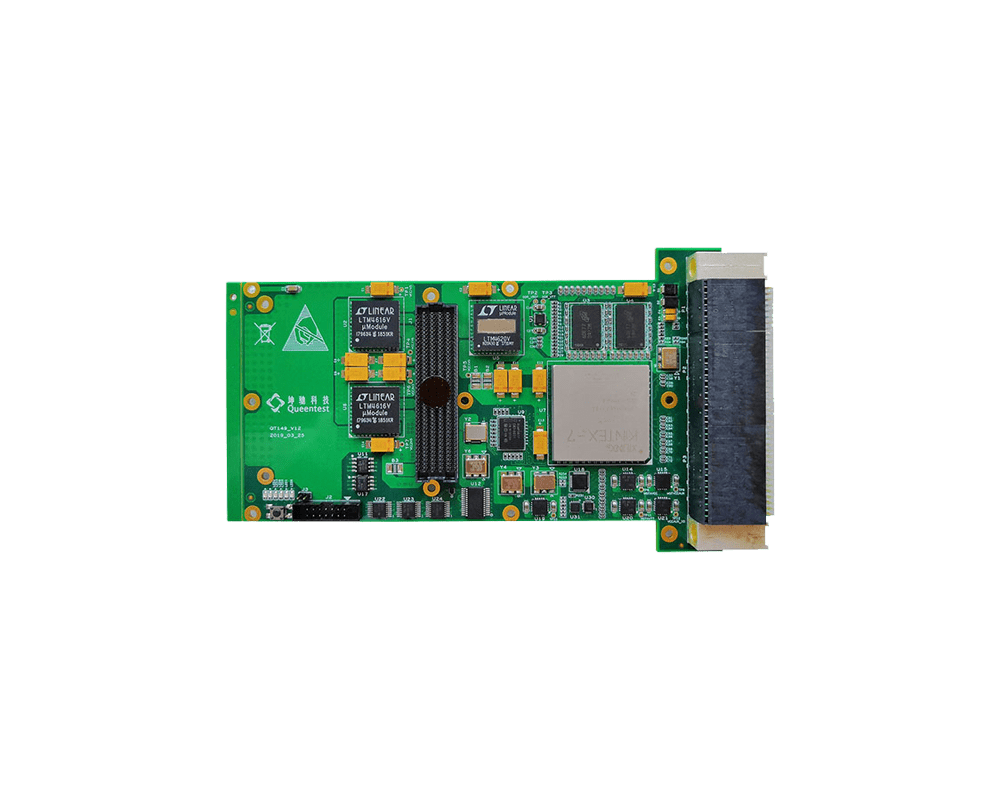

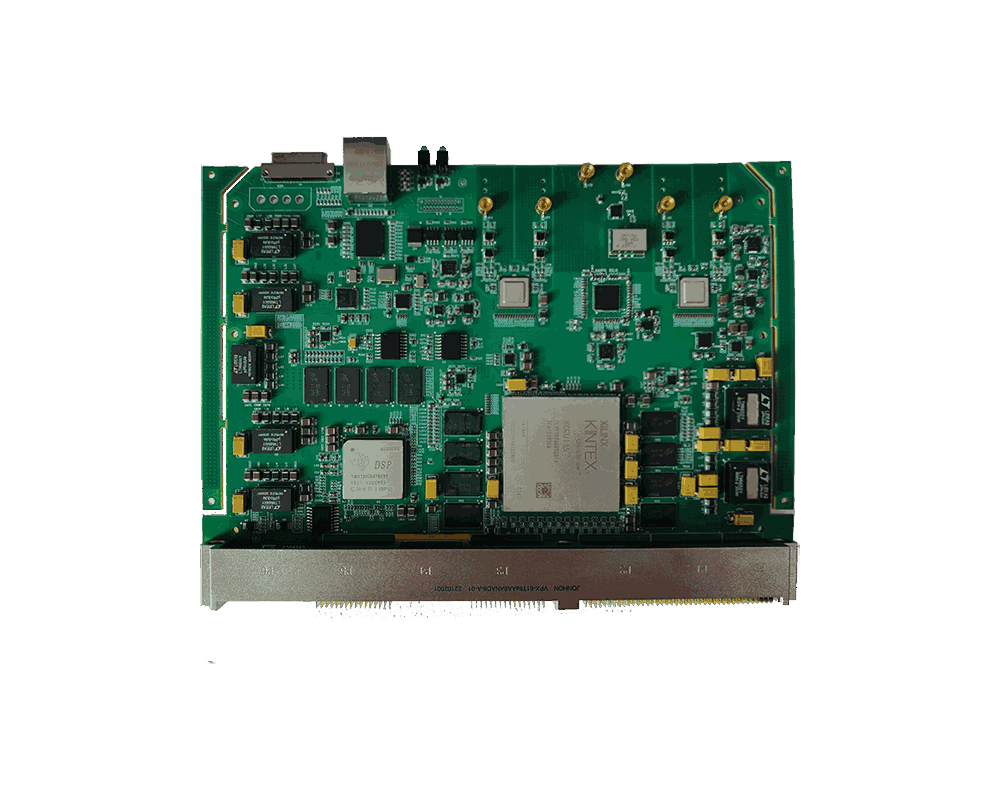

采集系统如下所示:

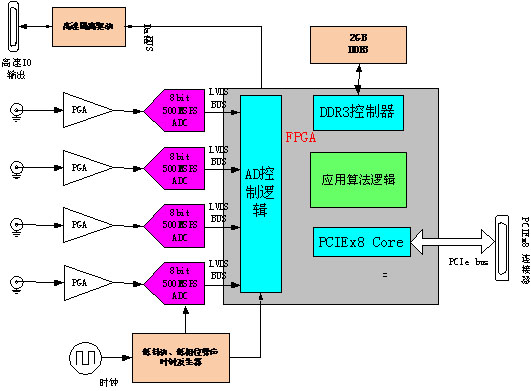

采集卡包括如下特性:

1.4通道8bit500MSPS同步采集。

2.4通道程控增益放大器,增益倍数0-100倍调整,满幅度输出1Vpp。

3.输入通道DC耦合,50欧姆输入阻抗。

4.模拟输入带宽DC-120MHz/-3dB。

5.输入端口过压保护,允许200W/20us浪涌功率输入。

6.2GB本地缓存,保证每次触发,每通道有0.5S的采集时间。

7.支持PCIEx8接口,连续数据传输率1000MB/s。

8.低抖动、低相噪时钟发生器。

9.可以多块卡组成多通道同步工做模式。

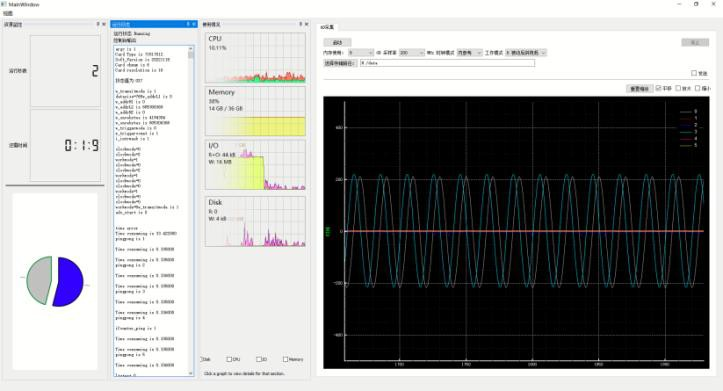

系统工作模式如下:

1.触发设置:可以根据输入脉冲的幅度和宽度设置触发判决条件。

2.输入放大倍数可以通过软件设置。

3.输出脉冲相对于触发事件时间可以设置,小单位为2ns。

4.出脉冲和触发事件条件随机延迟不超过4个采样点,及8ns。

5.触发后,采集长度可以设置,大每通道可以采集500M个点。

6.可以回传长度为500M个点的原始波形供计算机软件分析。

系统配套软件:

系统软件包括应用软件,二次开发API函数,以及FPGA开发环境三部分。

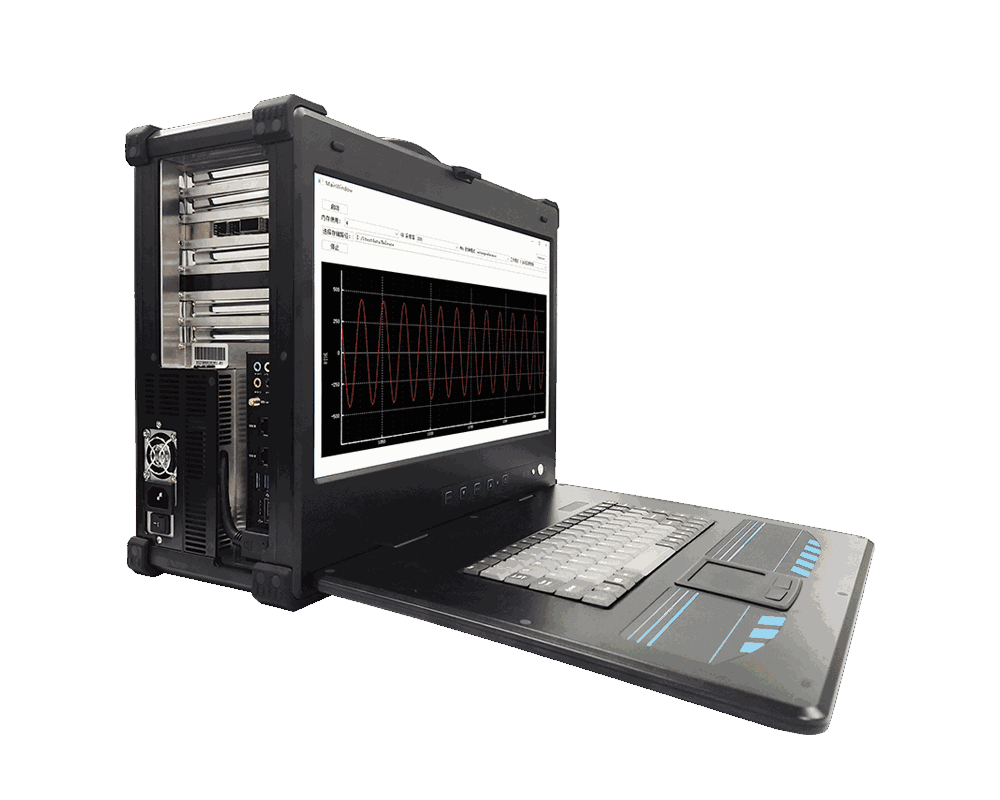

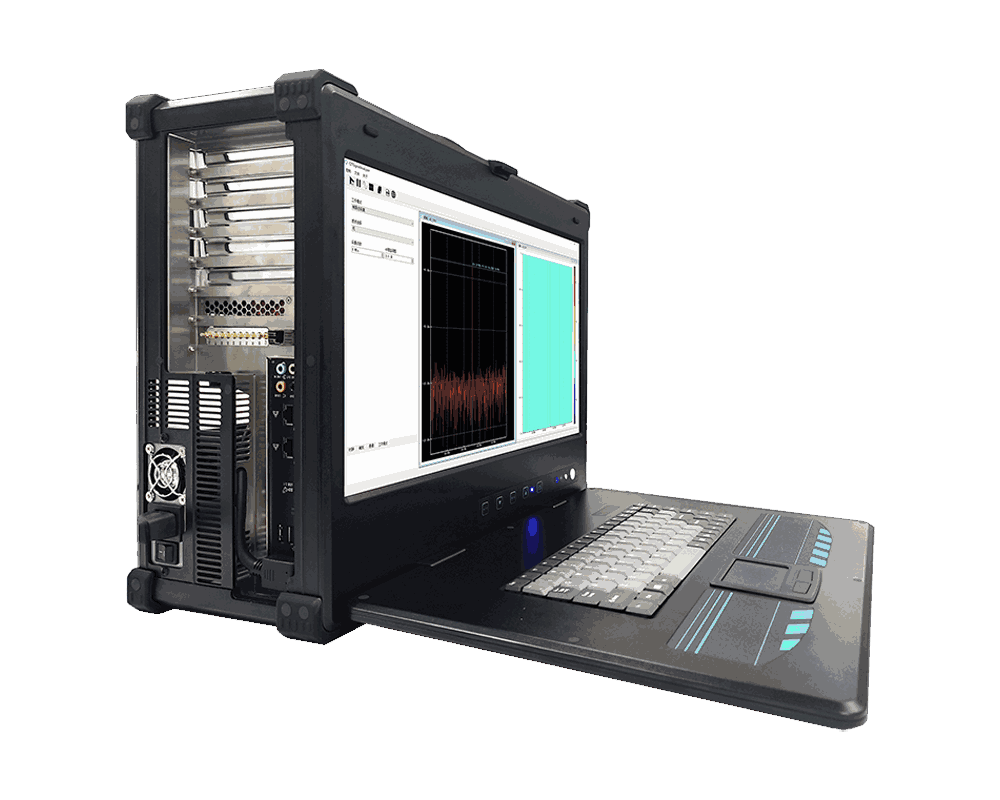

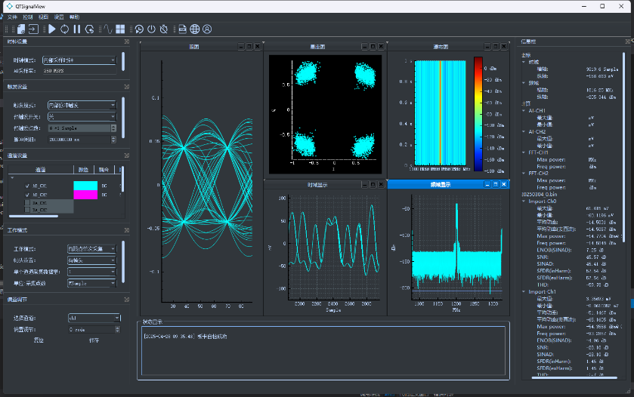

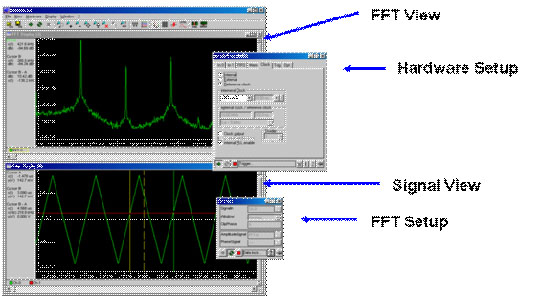

1.应用软件,具有虚拟示波器功能,方便设置硬件,读取/保存数据以及波形显示/频谱分析功能。

其功能和界面如下所示:

2.二次开发API函数:

我们提供丰富的接口函数和系统主要功能的例程,支持C/C++,labview以及Matlab环境下的二次程序开发。

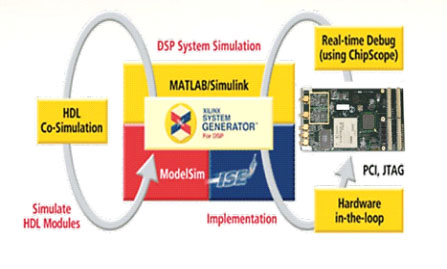

3.FPGA开发环境:

我们提供采集模块的全套FPGA开发工程,全部基于VerilogHDL或VHDL开发环境。用户逻辑只需要在目前已经建立好的工程中加入自己的RTL代码即可。

同时提供Xilinx的systemgenerator同matlab/simulink接口工程和实例。