脉冲信号采集方案

基于PCIE总线的脉冲采集方案

一、概述:

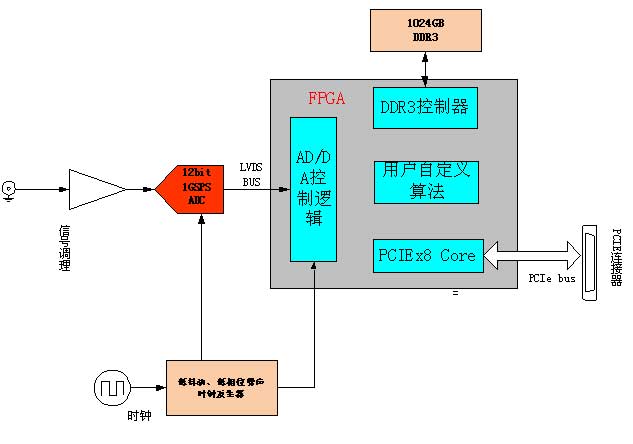

为采集高速脉冲输入信号,并能实施将采集数据传入PC主内存,系统方案规格如下:

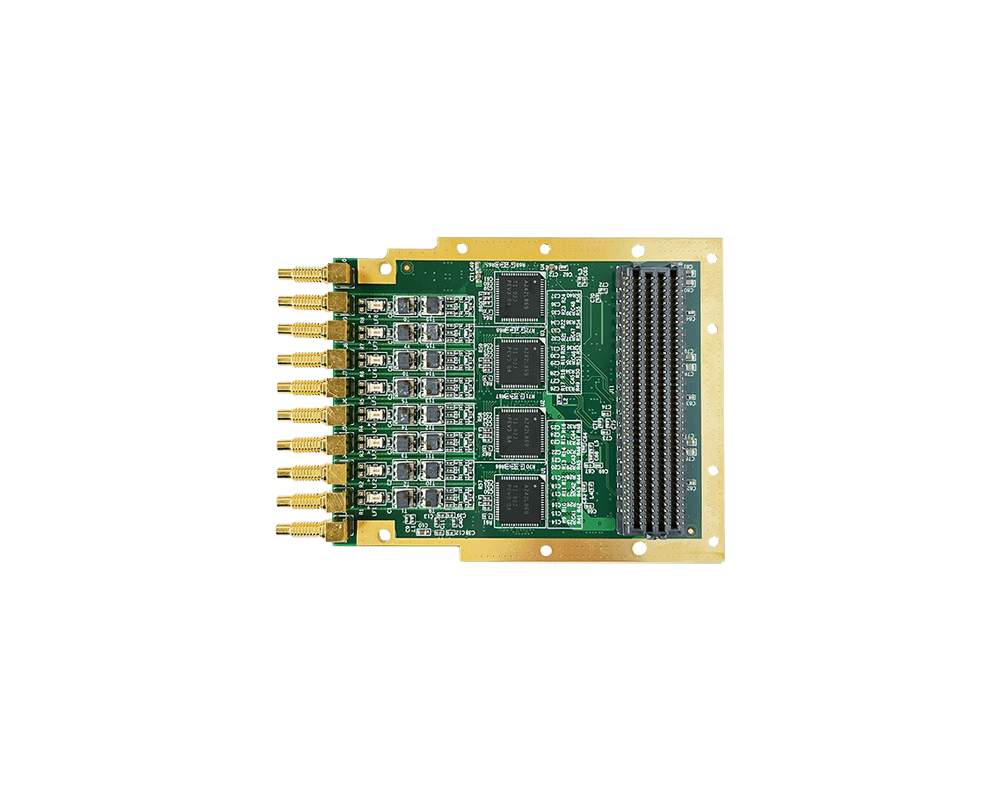

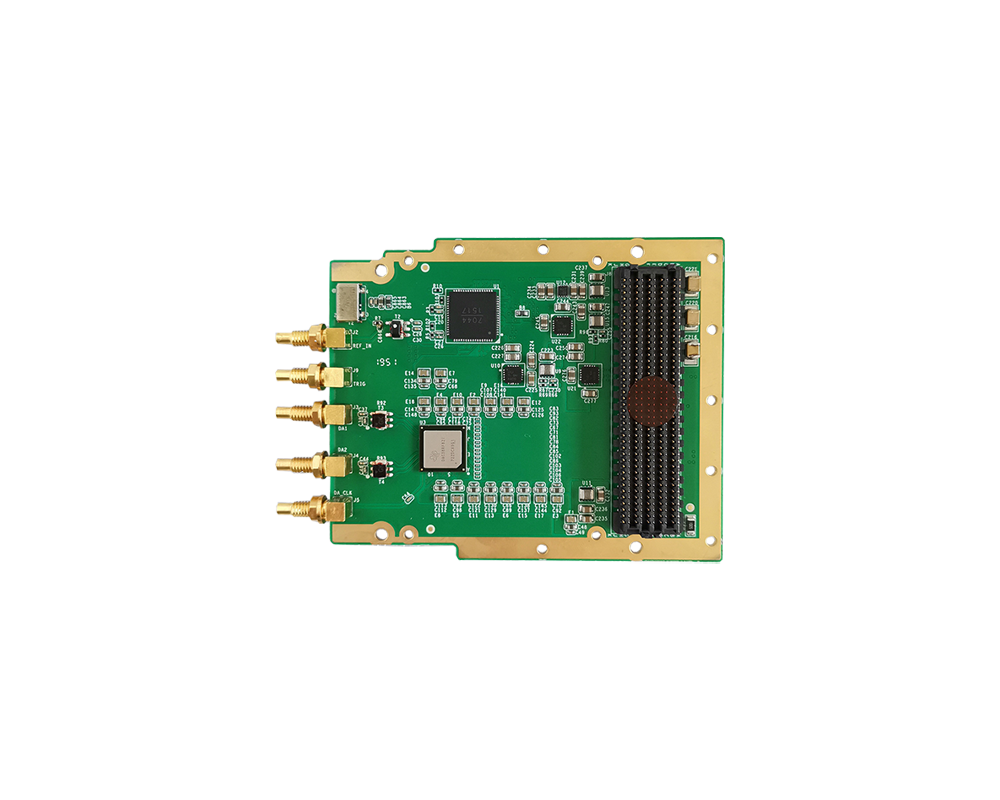

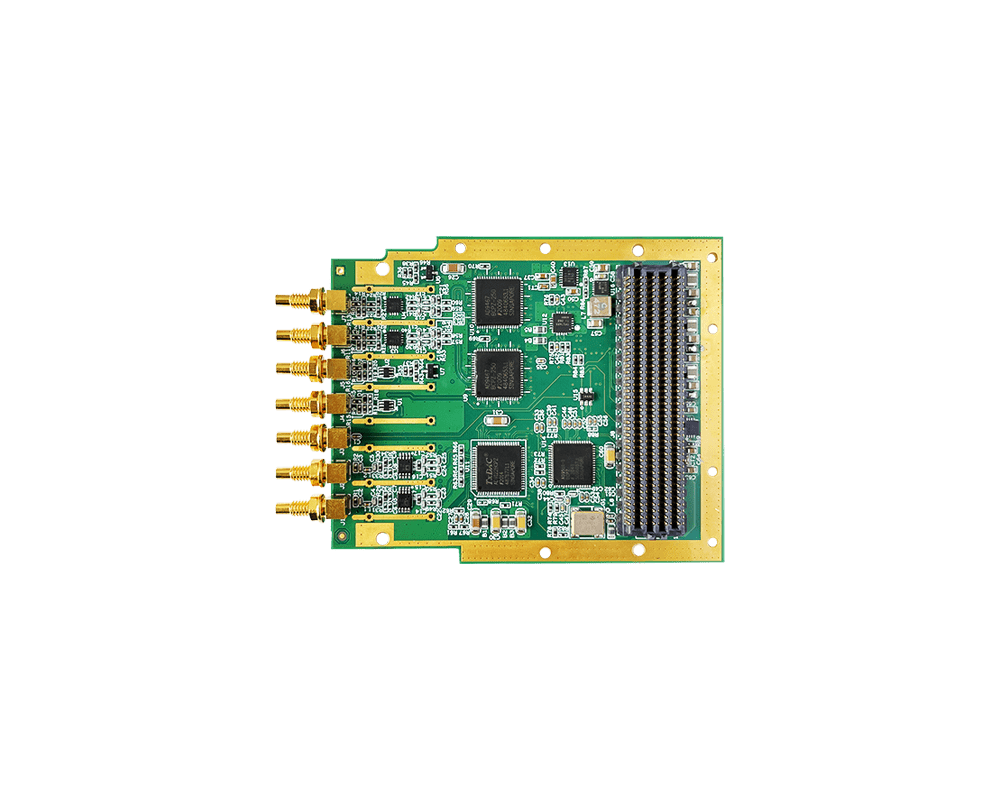

1.采用12bit1Gsps高速ADC。

2.50欧姆阻抗输入。直流藕合,输入信号范围0~+5V,输入模拟带宽大于500MHz。

3.板载2GBDDR3内存。

4.采用PCIEx8接口。

5.支持用户二次开发FPGA逻辑。

6.提供用户二次开发软件。

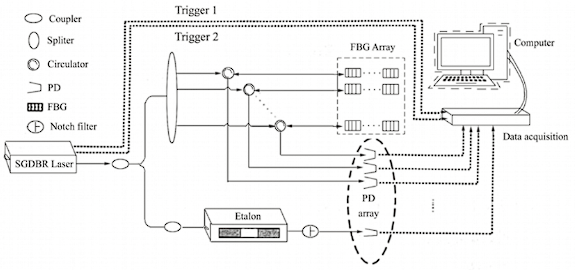

系统框图如下:

二、为了实时得到采集数据,在数据传输端,可以采用如下4种方案:

方案1:

通过设置触发门限,只采集有用信号。

在脉冲周期为10ms时,每个脉冲根据触发设置,采集3us左右(长度可以设置),约3000个采样点;实时传输数据率为600KB左右。通过PCIEGen1x8总线传输,DMA传输率为1250MB/s。

方案2:

如果需要实时传输采集数据,12bitX1Gsps等于2GB/s,需要采用PCIEGen2x8总线传输。PCIEGen2x8总线传输理论上支持3000MB/s的传输率。

配合高性能计算机,配置32GB主内存,理论上可以将2000MB/s的数据实时传输到计算机中。

方案3:

该系统支持FPGA二次开发,用户可以将算法通过FPGA实现。通过FPGA的实时信号处理,数据率可以大大减小。

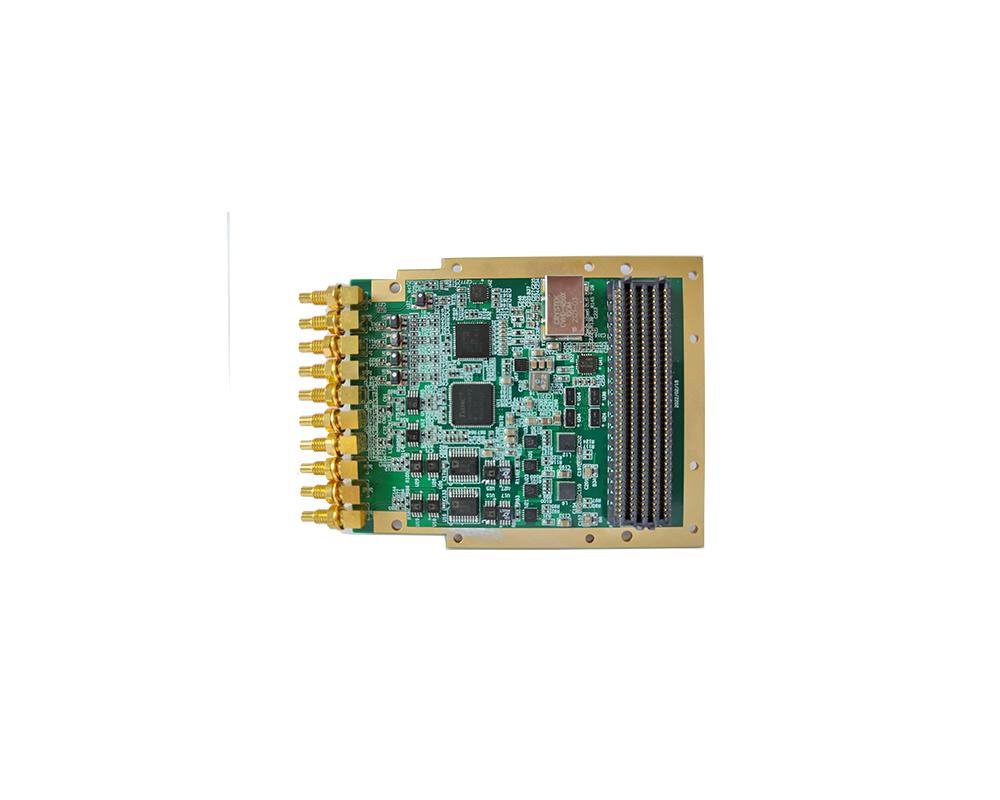

方案4:

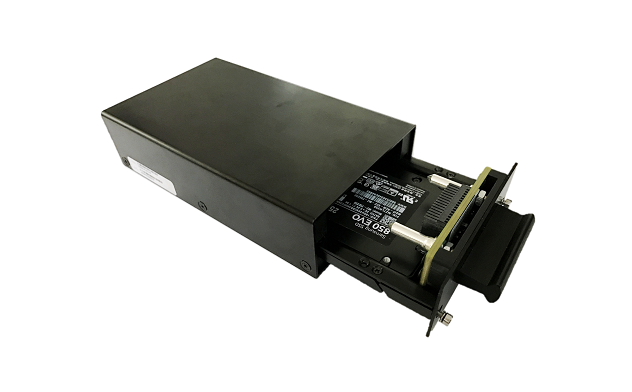

在采集卡旁边增加一块PCIE板,上面FPGA具有磁盘控制功能,能在机箱上连接8-16块SSD盘,实时存储速度大于2000MB/s。由于SSD磁盘容量较大,小容量256GB,大容量9.6TB,存储波形时间非常长。

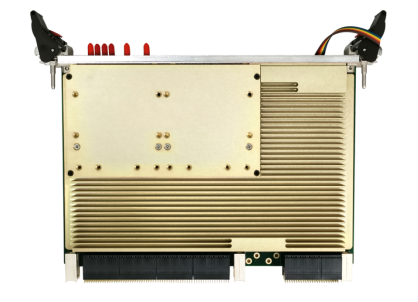

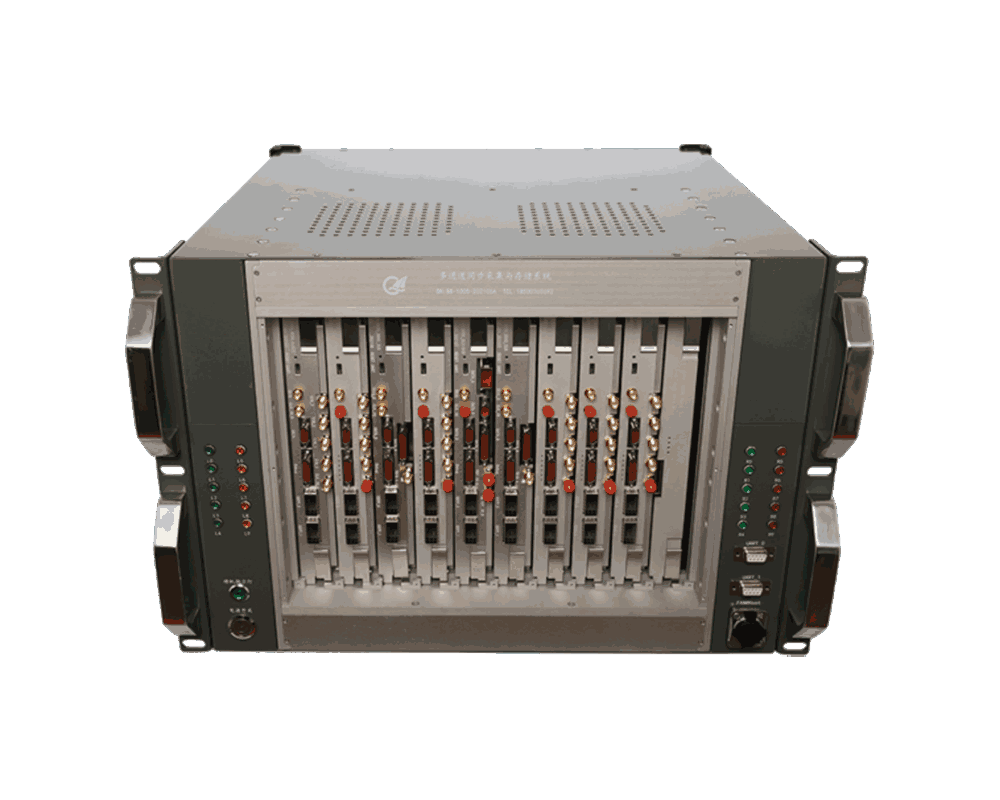

附图为磁盘储存样机:

方案对比表:

|

方案 |

技术准备度 |

后期开发工作量 |

成本 |

||

|

采集 |

FPGA |

PCIE总线 |

|||

|

只采集有用信号 |

需开发 |

少量开发 |

PCIE Gen1 |

只需开发算法 |

低 |

|

采集全部波形 |

需开发 |

少量开发 |

PCIE Gen2 |

只需开发算法 |

高, 需要高性能FPGA和 |

|

FPGA实时计算 |

需开发 |

大量开发, |

PCIE Gen1 |

软件工作量小,FPGA |

中, FPGA开发周期长 |

|

FPGA直接存储 |

需开发 |

少量开发, |

PCIE Gen1 |

软件工作量小 |

高, 需要格外增加一块FPGA-PCIE卡,需要外接32块SSD盘 |

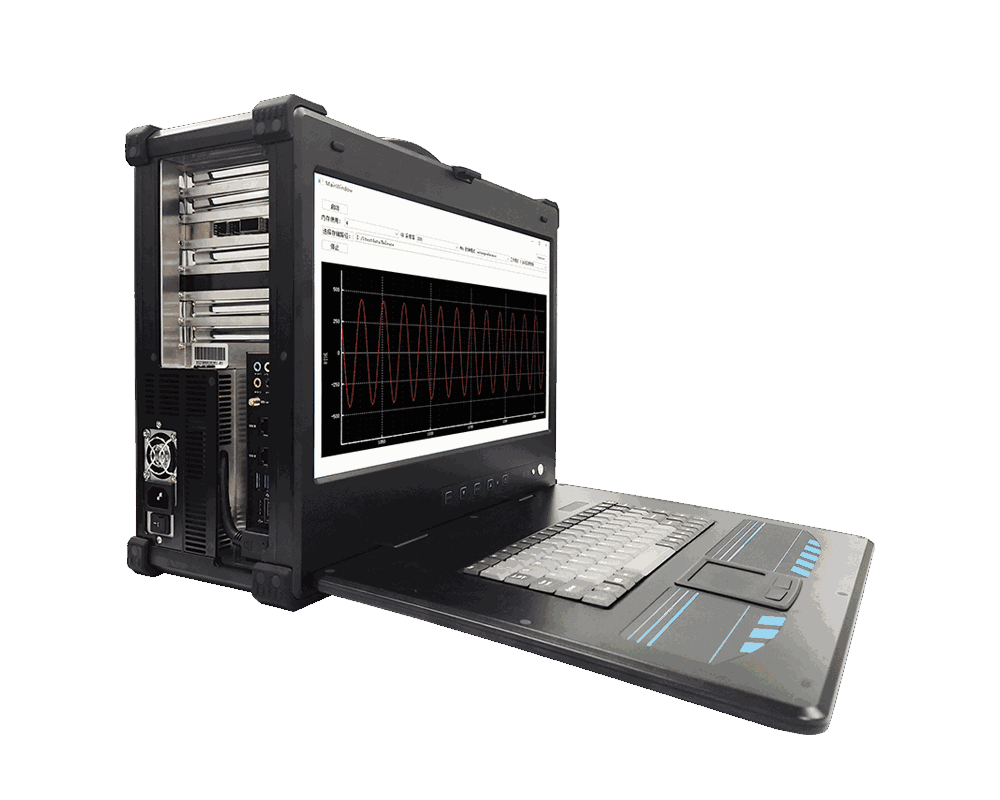

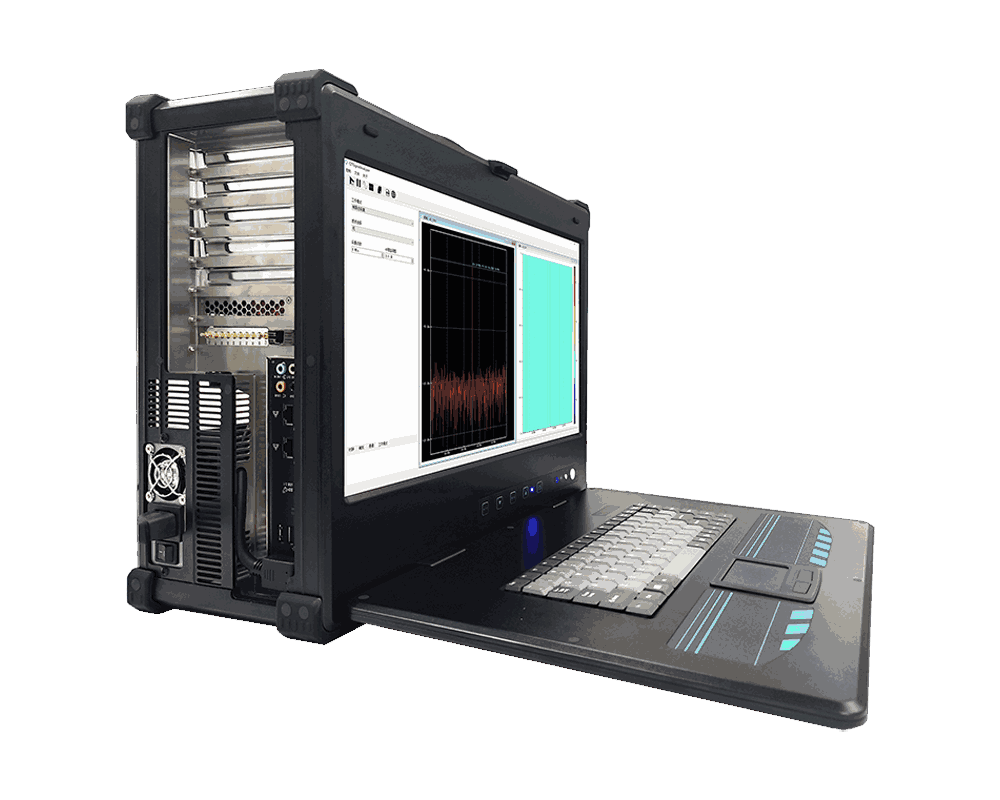

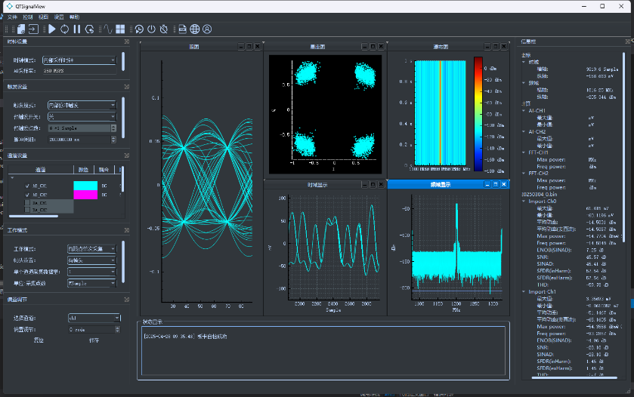

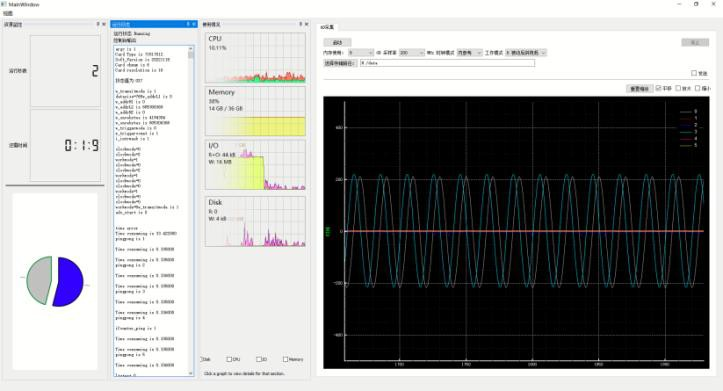

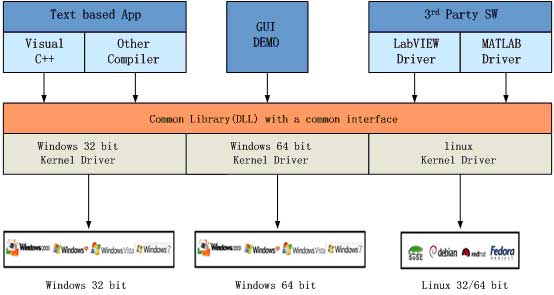

三、系统应用软件如下:

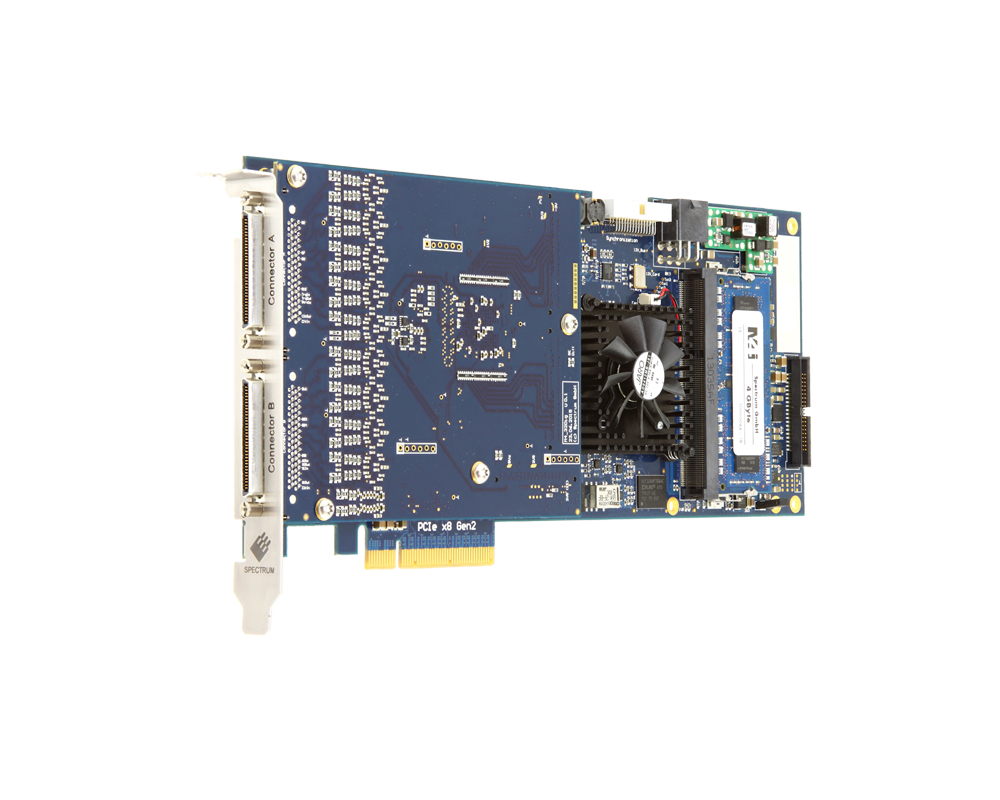

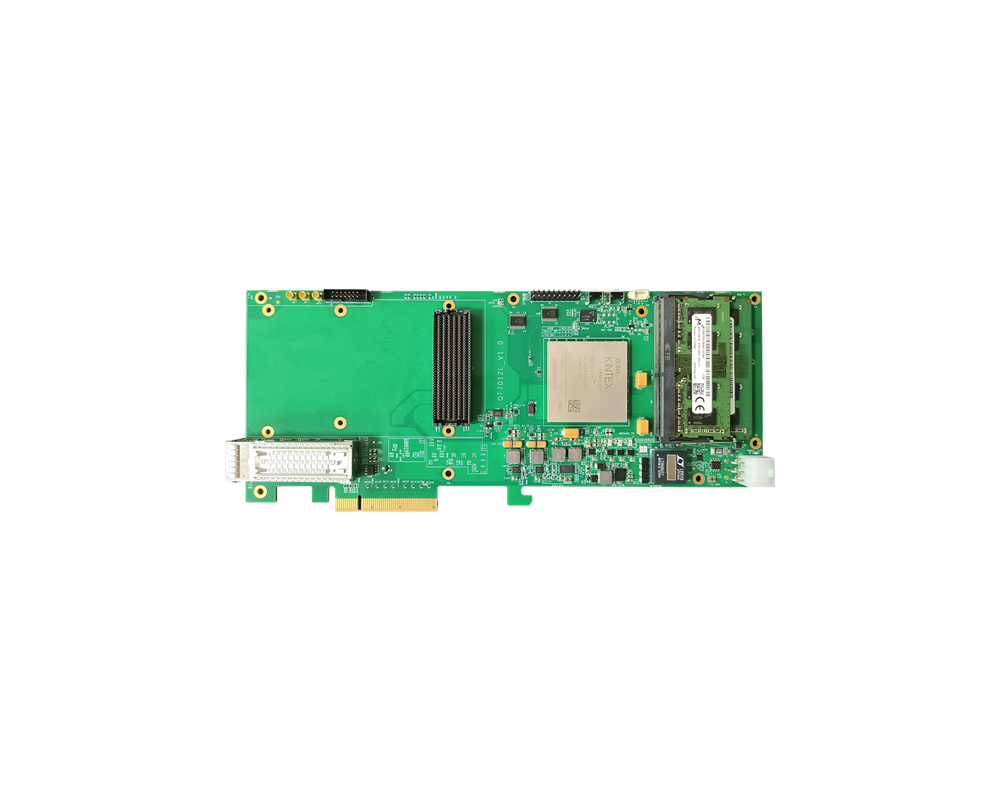

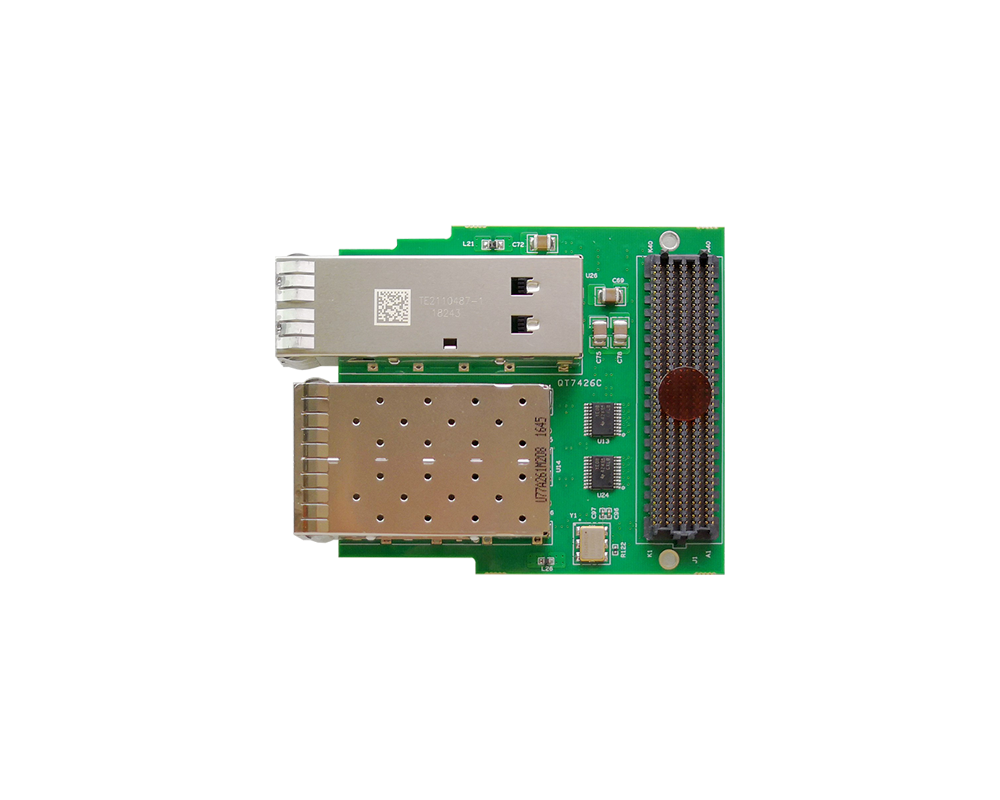

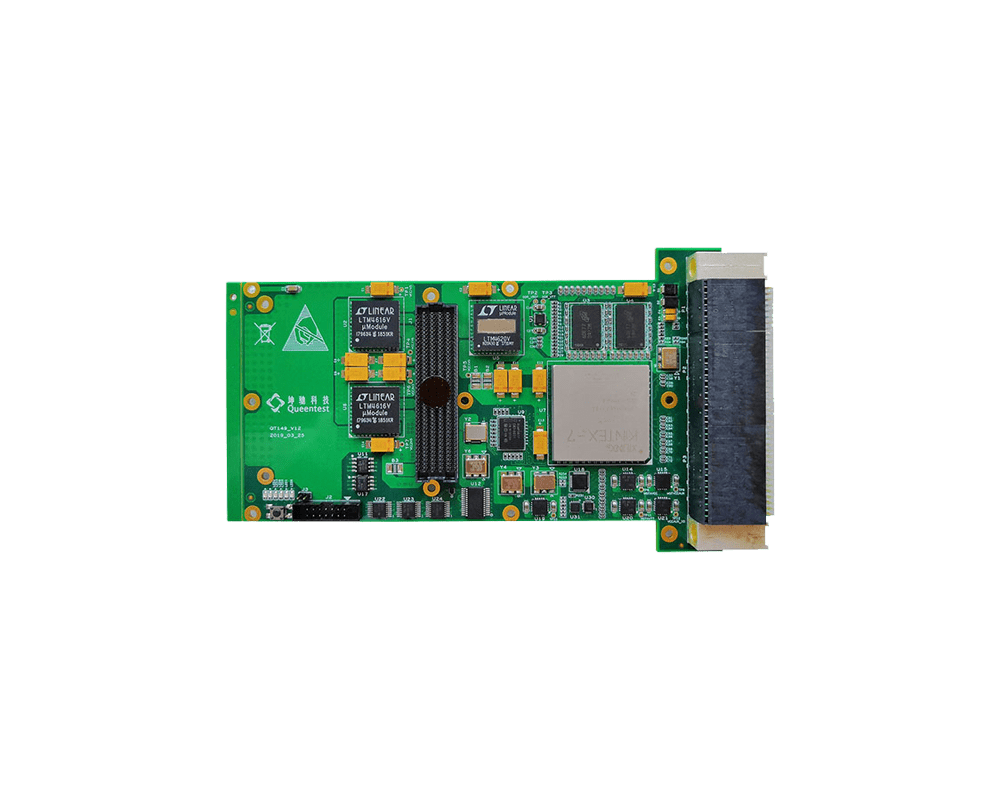

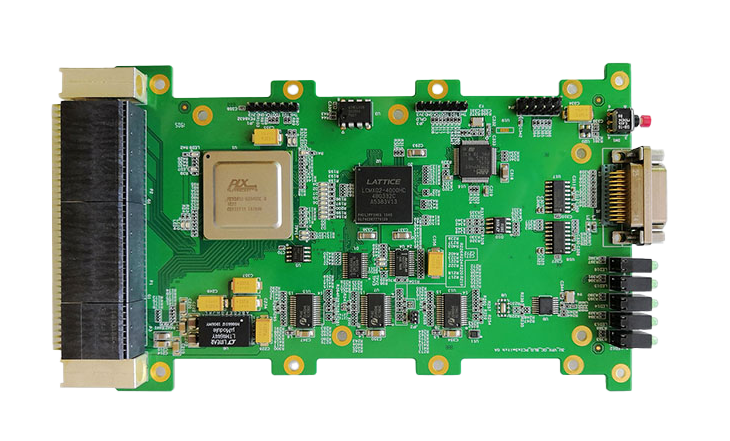

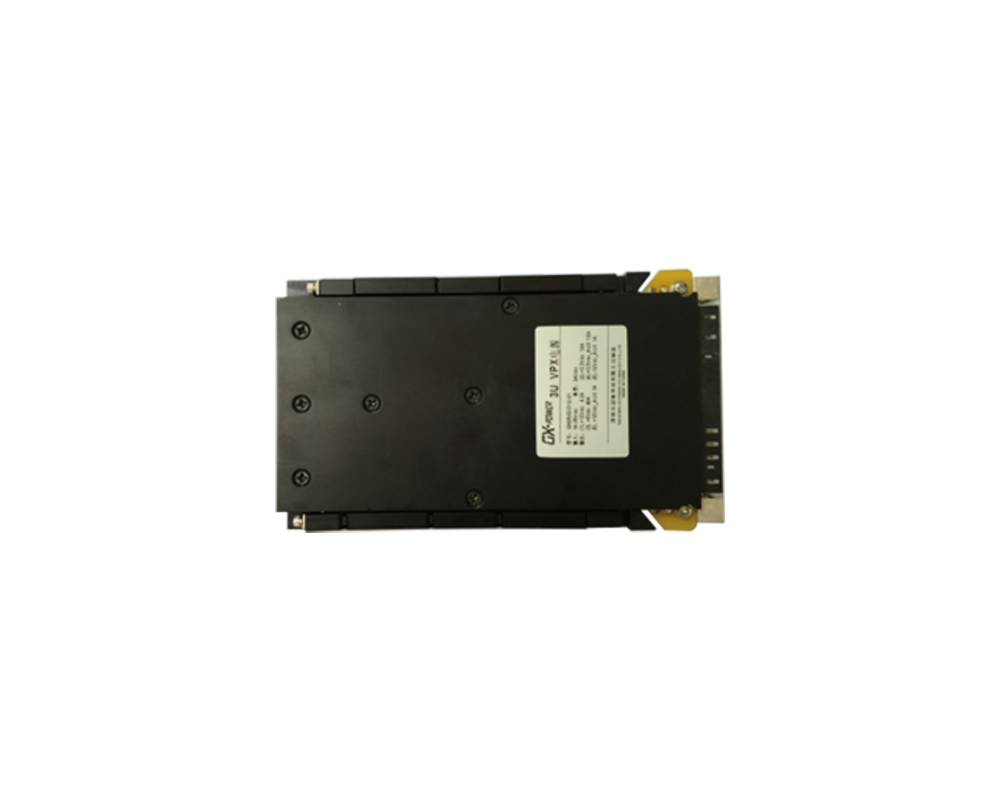

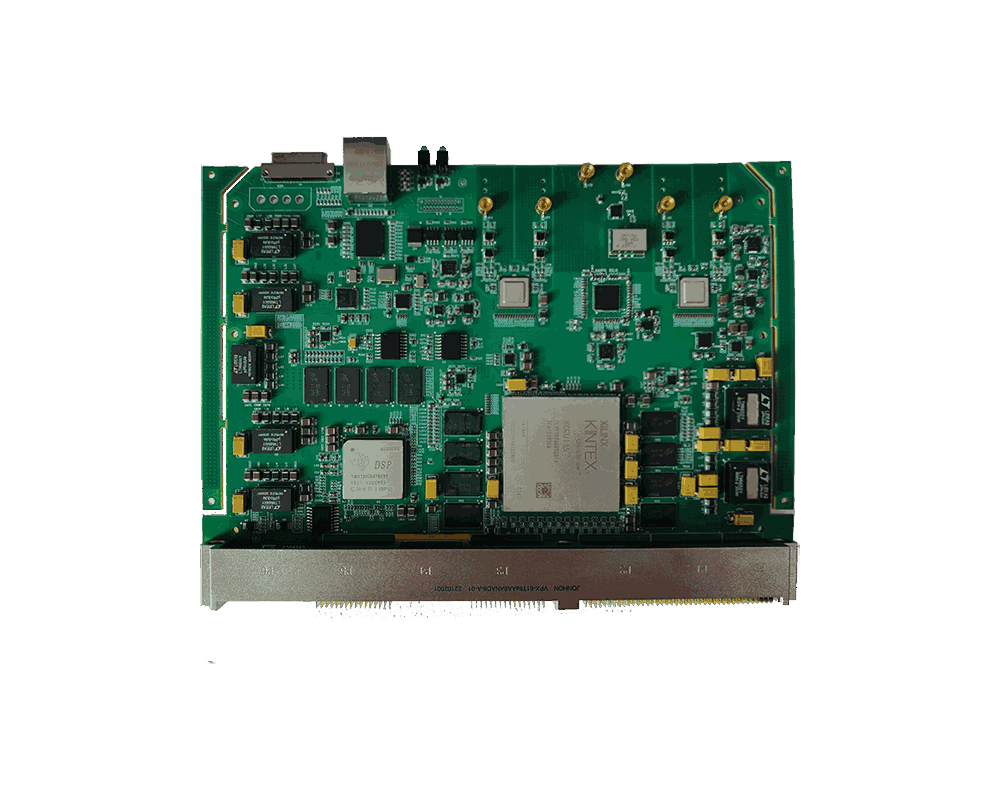

四、PCIE采集卡实际图如下: